模数转换器中的混叠:并不是所有的信号都像其看上去那样

你看没看到过汽车向前行驶,而车的轮子实际上是向后转呢?如果不是在表演高难度特技的话,我打赌你一定在汽车广告中看到过。你想没想过这是为什么呢?

真实的生活如流水般不可中断,而视频摄像头每秒钟只记录了有限数量的画面。每一帧画面可以捕捉到处于不同位置的车轮,而这也取决于在帧与帧之间车轮旋转的圈数,它们也许真的看上去是向后旋转的!这个效果被称为混叠。

使用模数转换器 (ADC) 的数据采集系统会经历同样的现象,原因在于这些系统对一个连续的时间信号进行了不连续的“抓拍”。在这篇博文中,我将简要介绍ADC应用领域中的混叠到底是什么样子的。

什么是混叠?

根据那奎斯特原理,为了在数字域内复制原始信号,ADC必须至少以输入信号最高频率分量的两倍对输入信号进行采样—否则的话,会产生混叠。所需的最小采样率被称为那奎斯特速率。或者反过来看,ADC能够准确转换的最高频信号为采样率的一半,这被称为那奎斯特频率。

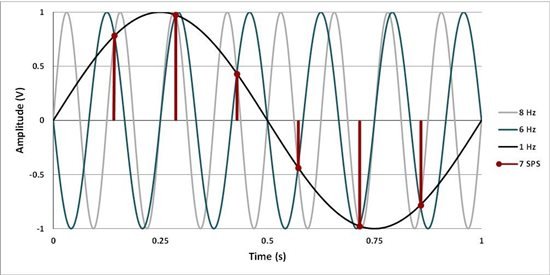

我们来看一个示例数据采样系统,在这个示例中,ADC以每秒7个样本 (SPS) 的速率对6Hz输入正弦波进行采样。我们得到的那奎斯特频率为3.5Hz,对于任何一个频率大于3.5Hz的输入信号,会产生原始信号的混叠。图2显示的是时间域内,使用6Hz原始输入,以及其两个混叠的情况:这两个混叠分别为1Hz和8Hz。由于全部3个正弦波在每个采样上相交,所以,以7SPS采样获得的6Hz正弦波看上去与1Hz或8Hz的正弦波没有什么不同!当我们查看输出数据时,混叠使我们无法将想要测量的6Hz 正弦波与它的混叠波形区分开来,并且所需要的信号内容也丢失了。

图2:时间域内的混叠

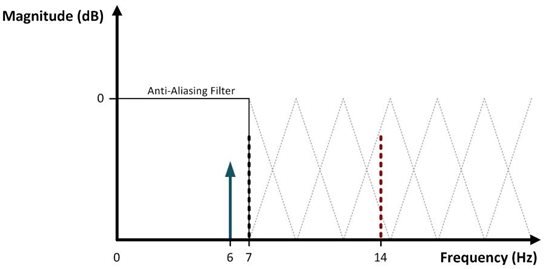

不过,你怎么能知道6Hz正弦波将会在1Hz和8Hz时出现混叠呢?在频率域内观察混叠会使得这一点变得很明显。当使用ADC进行采样时,输入信号的频率成分,从DC开始,在数倍于采样率的频率上重现。现在,你应该明白术语“折返”为什么经常被用来描述信号的混叠方式了—如果你沿着虚线将图3折叠起来看,这些信号互相之间完美地重叠在一起。

为了准确地测量输入正弦波,采样率必须满足那奎斯特采样标准。在上面的示例中,你需要将采样率至少增加到12SPS。恰恰在12SPS时,6Hz输入将仍然折返至DC,并且会在测量值中增加一个偏移,所以,采样只快了一点点,确保你所需要的信号根本就不会发生混叠。

不过噪声情况是怎样的呢?在整个频率范围内会出现白噪声,毫无疑问,白噪声将从更高频率混叠返回至DC与那奎斯特频率之间的通频带。产生的是一个更高的带内噪声水平,而这会降低信噪比 (SNR) 等重要技术规格的等级。幸运的是,有一个针对此问题的解决方案:那就是抗混叠滤波器。

抗混叠滤波器

大多数ADC之前都会有一个抗混叠滤波器,而这个滤波器与衰减信号(超过了所需带宽)的低通滤波器没有什么不同。如图4所示,一个理想抗混叠滤波器的响应在那奎斯特频率之前是绝对水平的,在这个频率之后,它迅速滚降,以衰减带外频率。在这里,采样率已加倍至14SPS,这将7Hz的那奎斯特频率和原始6Hz输入安全的放置在通频带之内。

图4:理想抗混叠滤波器的频率响应

设计一款能够实现这种频率响应类型的滤波器可不是一件容易的事,通常需要有源组件。这些额外的组件会大大增加信号链的尺寸、成本和功耗,并且很难达到理想效果。

为了使你能更好地理解上述内容,我将在随后的博文中介绍增量-累加ADC如何大大地简化了抗混叠滤波器的设计要求。此外,我也将提供某些适合你应用需要的抗混叠滤波器设计指南。

水军不懂帮顶。。。PS:玩模拟的连时域频域都要涉及了真是个悲催的活。。。。。。PS的PS。。。maylove姐好强大。。。无限膜拜中。。。。

因此前端采集都得加个抗混叠电路 即高阶低通滤波器

期待介绍增量-累加ADC如何大大地简化了抗混叠滤波器的设计要求

内置数字滤波器