PNP管驱动继电器和NPN管驱动继电器有何好坏之分

能不能借助着这三个图分析下。

应具体问题具体分析

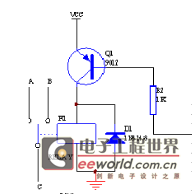

【例1】假如继电器和MCU共用5V,且MCU驱动脚在上电时的默认设置为输入+内置上拉,那么最好选择用PNP管共射放大器带继电器,这样能保证继电器在上电时不会有瞬间吸合误动作。

【例2】假如继电器和MCU使用不同电源,那么或许只用一个NPN管就能带继电器了。上例所说的上电瞬间误动作问题或可用加强力下拉电阻解决,若MCU的拉电流能力不足可用上拉电阻解决。

【例3】假如继电器和MCU使用不同电源,但希望继电器和MCU共地而需PNP管驱动,那么可再加一级NPN管做电平转移。

仅仅考虑晶体管和负载本身,采用PNP管还是NPN管驱动j继电器是没有好坏优劣区分的,完全等效,只要前级驱动足够即可。不过,如果是采用MCU的IO直接驱动的话,通常而言,MCU的IO为了双向兼容,往往低电平输出能力强于高电平输出能力,如果是这种情况,显然采用PNP管驱动为佳,晶体管是电流型器件,基极电流要满足负载驱动的要求。

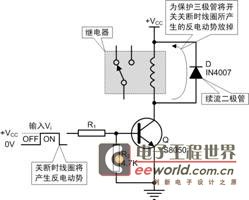

进一步考虑上电暂态的话,为了避免继电器在上电瞬间发生误动作,采用负逻辑即低电平驱动的设计更为有利,所以PNP管在此更合适。

不过前述因素都是基于MCU IO直接驱动的考虑,如果不是这种情况就要具体问题具体分析了,好的电路设计是要兼顾各方面因素以及基于整体性综合考虑的。

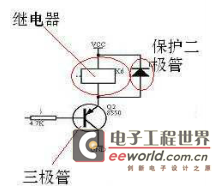

另外,就楼主给出的三个电路,其中图二(上面一行左起第二个图)是不适当的设计,该电路是射极跟随器结构,即使基极电位为0,射极电位也将是0.7V左右,而图一和图三是共射极开关电路晶体管的CE压降小于0.7V,别小看零点几伏的压差区别,在低压供电特别是电池供电的场合,差了这零点几伏很可能对继电器工作的可靠性产生不利影响,所以要特别留意,搞清楚晶体管基本电路的特性是很有必要的。

谢谢指点,我想问的就是IO直接驱动

谢谢仙猫的解答,非常的详细

继续提个问,管子如何选取呢?

如下几个方面:

1、参数,包括载流能力、耗散功率和耐压,应该留取至少50%的余量。

2、封装,根据你的需求选就是。

3、价格,尽量选常用型号,这样同样参数下更便宜。

我认为当MCU的IO口电压等于或大于PNP射极电压时,可采用PNP型;若IO口输出只有3.3V,而继电器需要5V电压,则此时采用NPN型驱动就不会有问题,而且现在的MCU IO口吸入或者流出1mA的电流是没有问题的。