个人觉得超级经典的电路!

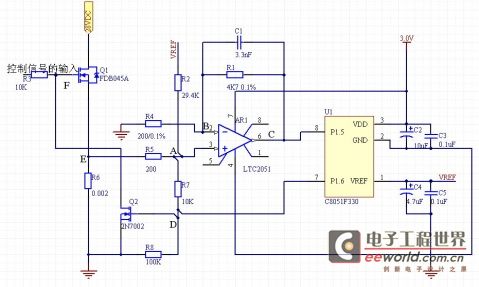

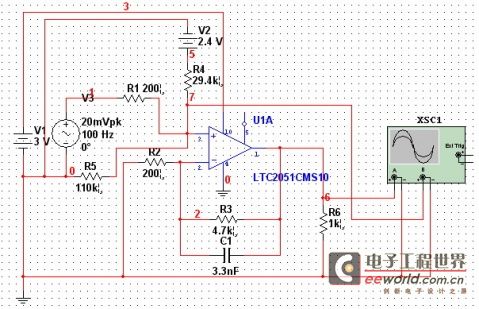

即将要分析的电路如下,这个电路本人觉得设计的很经典。这个电路主要完成的任务就是监测流经Q1和采样电阻R6中的电流。单片机C8051F330对电流的各种情况做出动作和反应。分析的主要部分不是在单片机内部结构和程序如何,而在于以运放为中心,整个电路的组织和联系。

图 1

在分析这个电路之前,我先简单介绍一下C8051F330单片机遇LT2051运放的接口部分的电器特征。首先,由于C8051F330内部具有10位高精度的A/D转换器。它的输入可以通过内部的交叉开关配置到P1.5端口。但是注意,输入的模拟量一点要小于3.3V,否则会损坏管脚。同时,C8051F330配置有内部的电压基准,可以供给内部ADC和DAC使用,也可以驱动输出至VREF引脚供外部电路。典型的输出电压为2.44V(VDD=3.0V)。P1.6端口通过交叉开关配置为通用I/O端口,具体配置是根据具体任务而改变的。

下面给大家分析分析此电路的经典之处。。。。

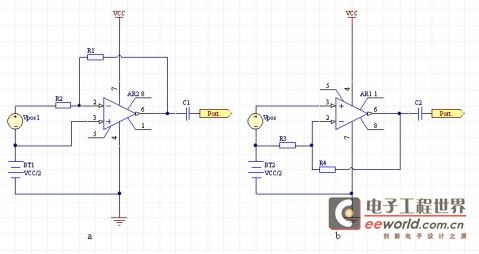

LTC2051是凌力尔特公司的一款双路零漂移的集成运算放大器。这款运放到底还有什么更好的特性,读者有兴趣可以自己去感受。这里,我只提到一点:它是一款Rail-to-Rail单电源运算放大器。也就是说,它的输出电压范围是满摆幅的即[0-3]V。它采用背靠背NPN和PNP输入晶体管和双折式共射共基放大电路使输入可达到每一个电源端点的几个毫伏之内。虽说轨至轨,但它不能在Uin=0时使Uout=0。所以,我们就不能像用双电源运放一样幻想着不采取一定措施的情况下输入为0的情况下输出也为0。为了控制精度,我们一般会在信号的正负输入端加各加VCC/2直流偏置电路如图2,这样的输出Uout= VCC/2+Aod*Uin。但是如果是从单端加入直流偏置,这样的偏置与信号一起被放大输出,Uout= Aod(VCC/2+Uin),如图3。

在单电源运放的应用中,直流偏置电压电路通常有三种:电阻分压法、运放电压跟随器法和射级电压跟随器法,如图4。读者可自行进行分析和选用。

图 2

图 3

图 4

从图1中我们也可以看出它是采用了最常用的电阻分压法,为运放提供单端直流偏置电压。这种电路不仅简单,而且成本低。但是,这种电源的输出阻抗大,输出电流的变化对偏置电压的精度影响很大。从电路图中可以看出它所提供的偏置电压并不是VCC/2,而是对单片机内部ADC参考电压VREF进行分压。另外,偏置电压的输出也不时VREF/2。因为是单端提供直流偏置电压,是要经过放大后输出的,而VREF/2太大了。经过下面的计算就可以知道这个值到底是多少。

计算之前,有必要交待一下此时P1.6端口的状态。对于C8051F330单片机所有的通用端口都是全双向口。所以,这里P1.6作为输入端口时,端口寄存器中的值不会影响D点电压,只作为输入。另外2N7002导通的典型门级电压为2.15V,所以在电路工作在正常状态时2N7002不会导通。不导通, Q1的高电平控制信号就是有效的,Q1就会正常导通工作。做了这些铺垫后,我们来看一下A点的电压怎么来计算。

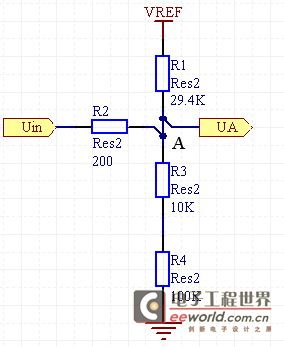

如图5,这应该是一个正向输入的运放加法电路。从电路计算依据上我们可以在A点应用基尔霍夫电流定理。

所以有:(Uin-UA)/R2+(VREF-UA)R1=UA/R3

为了方便起见,我们用R3代表R3+R4。

结果应该是:UA=R1//R2//R3(Uin/R2+VRER/R1)。

下面我们给它换个形式,即:UA=Uin/(R2/R3+R2/R1+1)+VREF/(R1/R2+1+R2/R3)

由于R2/R3<<1,R2/R1<<1所以Uin/(R2/R3+R2/R1+1)≈Uin。

式子△U=VREF/(R1/R2+1+R2/R3)中的各个参数都是已知的,最后计算出△U=16.2mv。

也即此电路图在输入信号的基础上叠加了一个16.2mv的直流偏置电压。这样即使Uin=0时,由于直流偏置的存在,输出电压不会是等于电源地,而是(1+RF/R)△U。从而提高了信号在0点附近的精度。

图 5

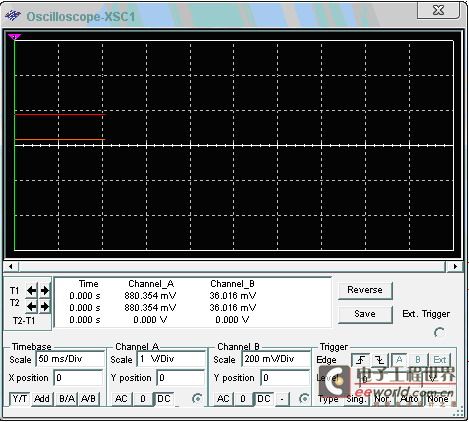

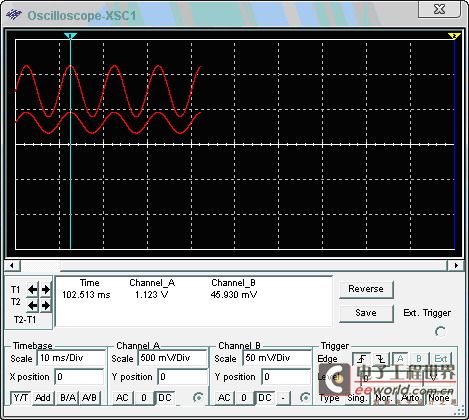

为了证明这一点,本人用MultiSim EWB 10做了电路仿真结果完全正确。如图6,正输入端的信号用50mv的电源代替,直流偏置电压用2.4v的电源代替。LTC2051的电源用3V的单电源供电。其中,示波器的channelA测的是U+,即信号与直流偏置分压后的叠加信号。ChannelB通道测的是运放的输出电压。

图 6

从图7中我们可以看到叠加后的信号刚好是20mv+16.1mv≈36.016。运放的放大倍数Au=1+R3/R2=24.5。测得的运放输出Uo=36.016*24.5≈880.354mv。依此来说明了以上分析是正确的。

图 7

刚才说P1.6是作为输入的,那么P1.6、Q2 到底是用来做什么的呢?我们来看,如果E点(也就是采样电阻两端)的电压是2.2V,则2N7002的门级电压(也就是D点的电位)就已经达到让2N7002的导通,并且P1.6端口的输入电压为高电平。一旦Q2导通,Q1的门级电压也就被拉低,Q1截止,使负载回路断开。也就是说O2、P1.6是负载电流的硬件监测电路。当负载电流到达一个极限值时,一方面硬件电路迅速动作,断开负载;另一方面告诉CPU采取必要的管理动作。

当采样电阻上的压降为0时,如果配置P1.6端口为推挽输出(能够输出10ma的电流),并且输出一个3v的高电平(VREF引脚配置高阻态),那么你猜A点电位是多少?很显然是3000mv*[R2/(R2+R5)]=58.8mv。我们也知道此时的Q2是导通的。这个就叫做BIT,即自检测功能。一个是检测运放、内部AD,另外可能也有采样值校准的功能。

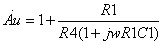

这个运放除了具有信号放大功能外,还是一个正向输入的低通滤波器。是通过C1、R1、R4的共同作用来完成的。好接下来分析一下它的幅频特性。我们用幅频域来表示放大倍数则有:

Au=1+Zf/Z1

这里的Z1=R4,1/Zf=jwC1+1/R1,所以有:

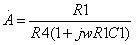

从上式中可以看出,对于信号的输出端总会叠加一个输入端的信号,无论信号的频率是多高。好我们只来分析后半部分,设等于A:

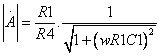

经过计算有:

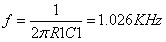

由上式可求出它的截止频率:

上述只是理论上的分析,接下来看一下软件仿真波形。这样可以比较直观的看到它对信号的放大和低通滤波的功能了。在仿真中,如图8所示用幅值为15mv的交流信号来模拟高频干扰信号,15mv的直流偏置模拟有用信号。通过仿真来现实的感觉一下这个电路时如何对信号放大和如何抑制高频干扰的。其中,示波器的channelB测的是U+,即信号与直流偏置分压后的叠加信号。ChannelA通道测的是运放的输出电压。如图9,先来看一下干扰信号为的频率100Hz是的运放输出。此时,是有用信号和干扰信号叠加后为零点,只剩下了VREF提供的偏置电位16.1mV,输出电压=16.8*24.5=394.556mV。图10是有用信号上叠加了干扰信号的正半周期,所以此时的输入信号应该是=30+16.1≈45.930mv,输出电压45.930*24.5≈1.123v。可见在干扰信号为100hz时,并没有明显的抑制效果。

图 8

图 9

图 10

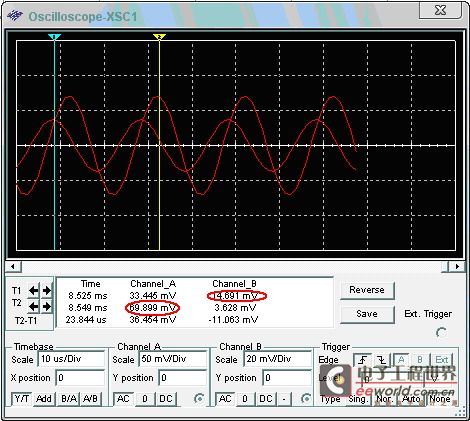

接下来将信号的频率改成50KHZ,看看它的滤波效果。如图11,将输入信号的直流偏置(模拟有用信号)和VREF提供的偏置在显示部分去掉,只显示交流部分,输出信号也同样处理,这样看起来更加明显。在图中可以看出在输入信号为14.691mv时,输出信号只有69.899mv。放大倍数为4.76,衰减了14dB。当干扰信号改为500khz时,由图12可以看出,输出信号就只剩下直流分量了。到现在为止,我的分析就全部完成了。经过这样一个完整的电路分析过程不仅对这个电路有了更深了解,而且让我学习和了解了更多的模拟电路的知识。很有意思。

图 11

图12

给力 呵呵

讲解的真不错啊

真好,收藏了

谢谢分享了

看看

谢谢分析!

讲解的很详细 顶个

bucuo ,dingyixia!!!!

用单片机来做反馈保护,要经过 T采集 + T判断 + T输出 才能对Q1进行切断。这种方式在保护的反应速度上不能保证。 使用直接电路反馈切断方式还是要有保证的多。

十分感谢楼主,分析的很好

很专业,楼主辛苦了,