SAR ADC 动态失调问题

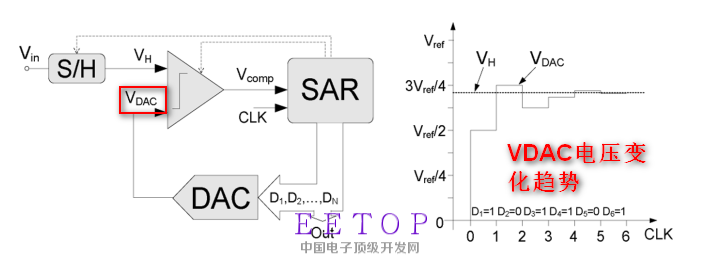

如图所示,如果不用CDAC采样,并采用单端模式,比较器的输入共模一直发生变化,因为有限的共模抑制比的原因,这会在输入端引入动态失调,如何解决这个问题?各位大神

如图所示,如果不用CDAC采样,并采用单端模式,比较器的输入共模一直发生变化,因为有限的共模抑制比的原因,这会在输入端引入动态失调,如何解决这个问题?各位大神

去ieee 搜索,single-ended, sar adc, 有几篇论文不错的。

對這個議題有興趣,可不可以列出來paper,因為沒辦法下載

能否给出相应的文献,对于单端SAR而言,常见就是利用失调存储解决失调电压,但是这只能解决初始时刻的失调电压...我目前准备做一个特殊应用的ADC,所以只能用单端

有点意思,值得研究,帮顶!

差分对的gm线性范围是根号2倍Vdsat。我建议把差分对的Vdsat调大试试,比如200-300mV

仿真看还有一个因素是尾电流变了,所以尾电流一方面要加大L,另一方面要加cascode管子

如果使用CDAC采样,在转换过程中也存在动态失调。我一般是把比较器的速度和放大倍数都增大,保证动态失调很小,不影响线性。

SAR ADC 动态失调问题

尾电流源使用cascode结构,这种方案确实是代价最低的

如果使用差分结构以及CDAC采样,共模就是固定的了

利用传统的失调存储,仅仅能解决在固定VCM情况下的失调,如果共模电压发生变化,也是难以解决

这其实就是提高运放的共模抑制比,是否也就意味提高运放增益(使用多级运放)

在使用差分结构时,输入差分信号,DAC输出共模固定,但是比较器还是存在动态失调。动态失调主要由两个原因造成:1)输入共模变化;2)差分电路寄生不匹配;

应该是这个意思,保证增益,同时也要保证带宽。不然就算增益很大,动态失调还是会存在,这时不是受共模变化引起的,而是由内部节点的“记忆效应”引起。

一般有限的共模抑制比是由MOS的不匹配和电流源有限的输出阻抗导致,假设匹配性能很完美的情形下,对于记忆效应以及带宽的影响,是否可以考虑认为,尾电流源的寄生电容导致高频下输出阻抗降的很厉害,从而高频下的共模抑制比很差。这有点像电流舵DAC的设计