请教,同一张wafer上不同dies的LDO输出差异很大,可能的原因?

请教各位大侠造成这种情况可能的原因除了mismatch导致bandgap输出漂移以外,还有没有其他的原因?

低端产品,偏差大点不影响应用,所以没做trimming。

有多大?比如输出1.8V,偏差多少?

设计3.2,输出2.8~3.6

一般做个+/-5%,好一点可以做到+/-2%

这个确实大了一点!设计应该有不足之处。

首先确认基准,其次LDO的误差放大器,还有就是反馈电阻是否匹配

如果输出稳定的话(没有震荡现象),感觉只可能这三处问题

关于ea的要求能具体一点么?窃以为EA增益不足的话PSRR会比较弱,但是测试结果这一项倒还好。其他还会影响什么呢?

如何实现,求指教。

基准设计时仿真可能是0.2%~0.5%的误差或者说离散,实际流片可以做到2%~5%以内的离散

EA一般保证60dB以上即可。

反馈电阻的匹配要做好。

这样出来的片子2%-5%没多大问题的

还有你的芯片离散是标准的正态分布吗?以3.2为中心,两头各占多少百分比?

不知道你能否测试基准的电压,首先要知道基准是否离散很大很大,基准的分部如何?

PSRR多好呢?@1k和@1M分别多少dB?

基准用到op了么?没用正常,用了就是你设计的问题了。多少的工艺。

用了,0.5的。

晶圆刚到手,还没有全测。

没搞基准的debug PAD。图省面积了,囧。

说错了,不是PSRR,是电源调整率,测PSRR要频谱仪,没搞。

你是在wafer上测试的吗?

电流模式的基准或者banba cell,还是其他的。0.5um工艺Vth 引入的offset很大,设计时要注意。

小编最好可以把你BandGap OpAmp和EA的结构上个图,差分对和电流镜的尺寸是多少,可以估算一下你的Offset贡献是多少。不然只能是猜测。最大可能是你的BandGap OpAmp的Offset太大了。如果Offset有10mv,被放大30倍,就有300mV了,也差不多10%的误差了,再加上EA的Offset,和你的结果差不多。

我想你这个Part,为了省面积,Offset应该很差。

另fuyibin and semico_ljj,不做Trim,想做到2%的精度也不容易吧。OpAmp的Offset不好做吧。一个专门的通用运放,没做校准和Chopper,Offset做到3mV已经挺不容易的了。在低成本的LDO中不可能花那么大面积做那么大的OpAmp。

"不做Trim,想做到2%的精度也不容易吧" 我觉得是否是指0.5um工艺如此。

再往下,0.35um,0.18um等,好像也不是很难。做的细致一些即可。

只知道大家设计设计体会是否如此。

0.13um,90nm等以下的可以较容易实现low offset,但是单片小面积的产品不会用到这类工艺,所以你和他们说的都对,但是你们的依据工艺不同。

是的。

kuijk cell(就是op+pnp,这个名字还是你教我的)。

你用kuijk cell也能产生那么大的偏差!应该是设计问题。

你说的很详细,谢谢。

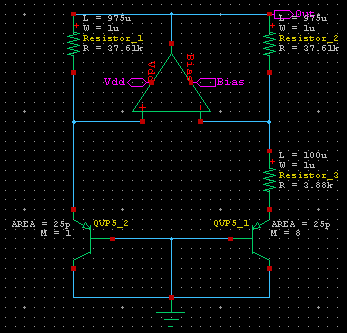

电路的结构极简单,如图。拍砖请轻拿轻放,谢谢。

这次电阻也没有做很细致的匹配,综合你所说的原因,应该差不多了。

可能版图上做的匹配不好。未必是设计的问题。

hszgl,你这个OpAmp就是BandGap上用的吧?按照你这个尺寸估算,如果是0.5工艺,OpAmp的1 sigma Offset就有4mV了,3 sigma Offset就12mV。你的PNP取值为1:8,那从OpAmp输入到Bandgap 1.2V输出大约offset被放大10倍,基本上就是10%的误差了。

semico_ljj,我说的确实是0.5工艺,0.35,0.18工艺确实offset会同比例下降,但Head Room也下降了,相对来说,信噪比还是没有下降。我到是没有用过0.18工艺下的5V器件,Offset参数与栅氧厚度成比例的,Offset应该和0.5u工艺一样的吧?而不是和0.18u低压工艺一样吧?所以对于小编的产品,都应该是在0.5u工艺平台看吧。

设计上的相关性可能更大。还有你是怎么测的输出,负载条件,电源电压,ldo本身的dropout值等测试的条件希望给出。

基准中的放大器输入管和下面的nmos你的m值都用1?