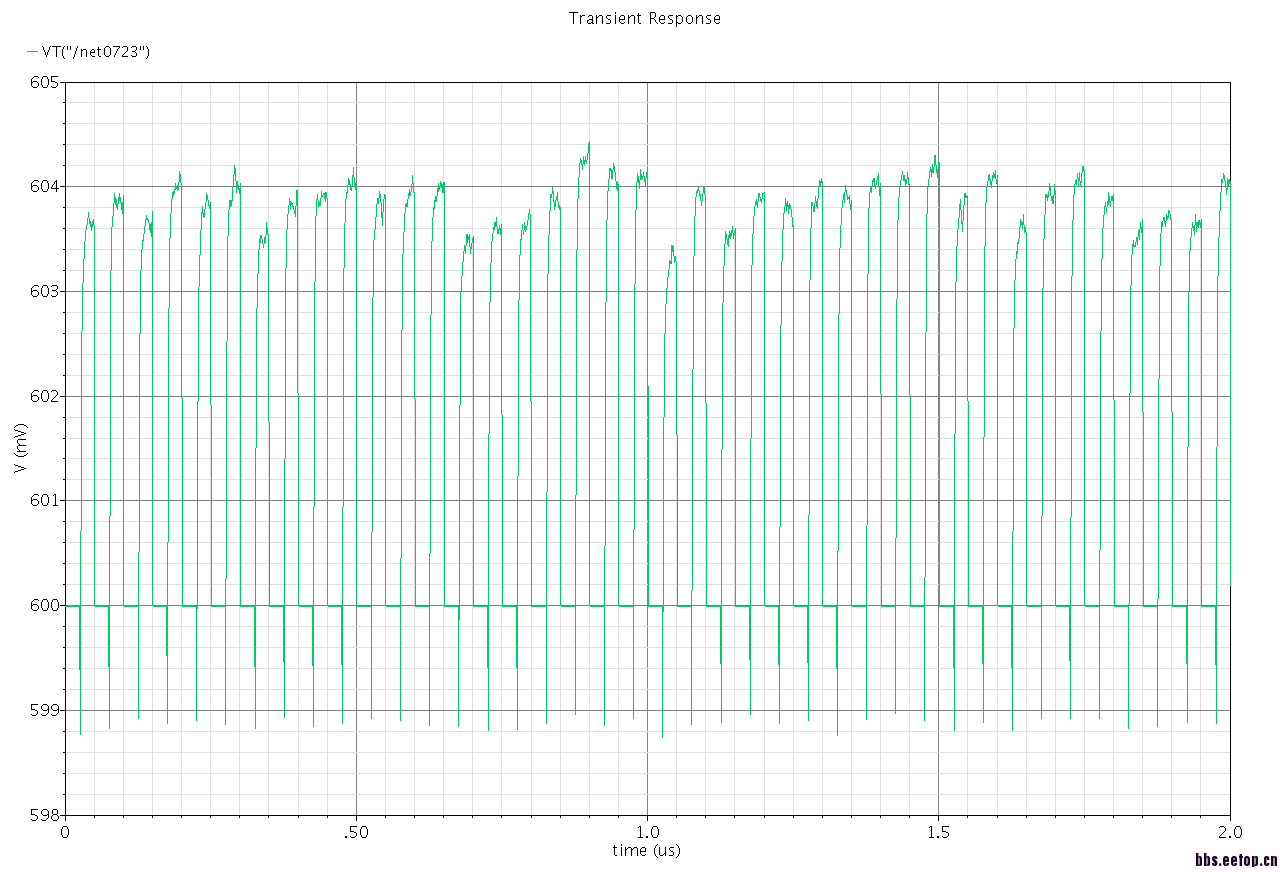

transient 仿真加noise之后完全惊呆了。

inveterinside

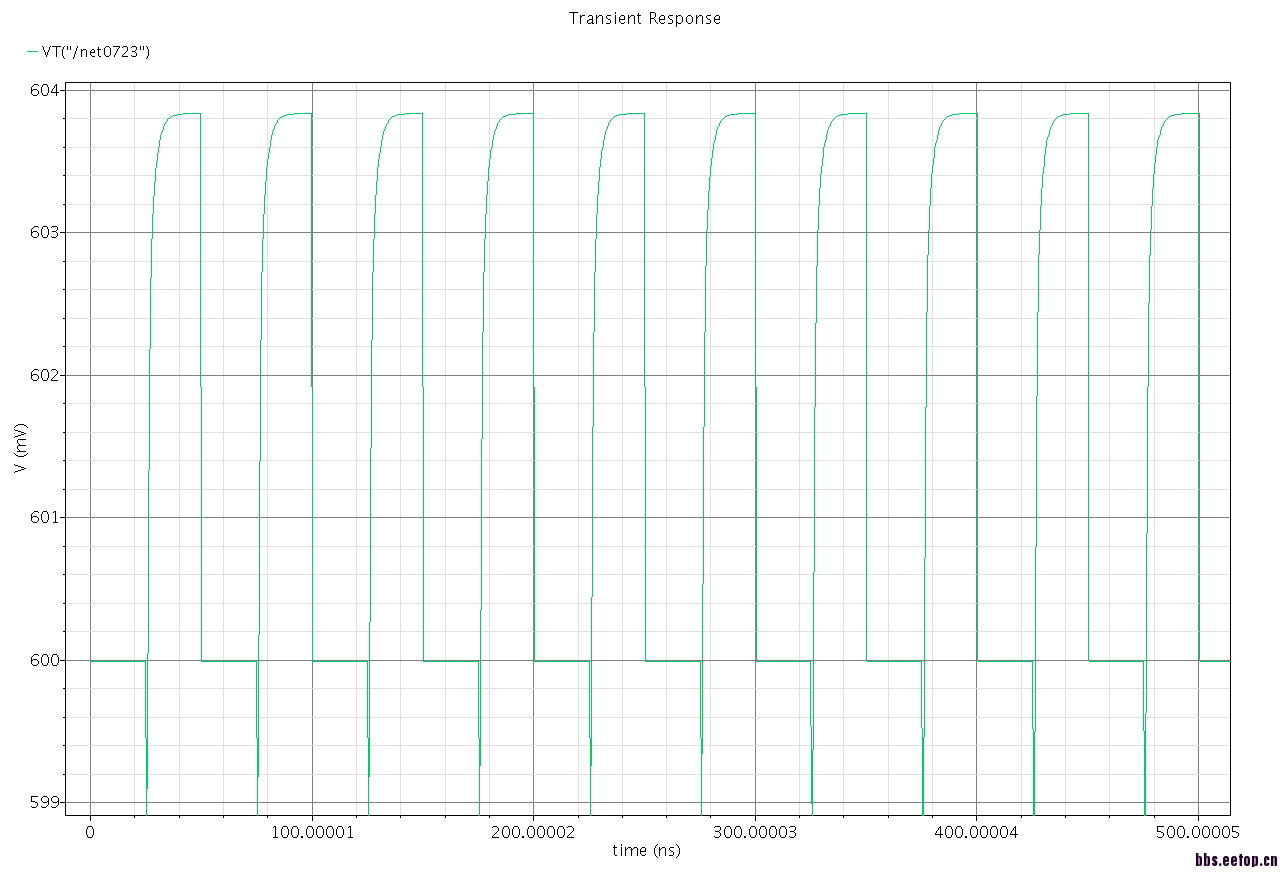

withoutnoise

withnoise

自己顶一个先,求启发。

加入的是transient noise?

是阿,不知道怎么解决这个问题

不就是噪声影响的吗

预期噪声使得输出在一个水平线上下震动,现在这个水平线都在不断的动,当然是噪声影响但是不知道是什么机制导致这个水平线的震动。

sample 到不同的噪声电压,使得在每一个hold阶段的电平不同

peak to peak noise也就1mV , rms值也就是0.1到0.2mV

也就是说,其实这个“增益跳动”是在KT/C限制之内的?好无知。

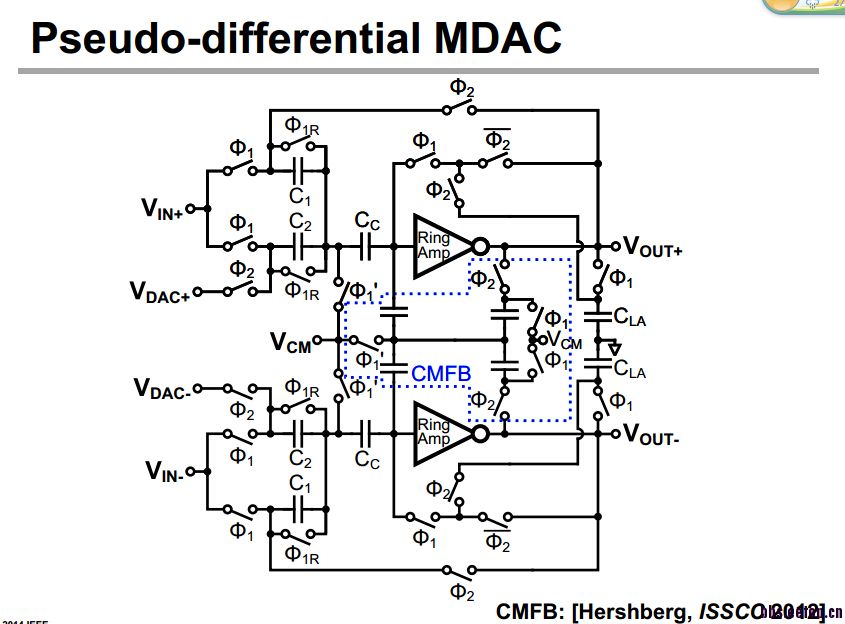

但是文章中用了同样数量的采样电容(400f=Cs+Cf;Cs,Cf 是这个MDAC中的采样,反馈电容),同样的放大器做出了一个SHA,作为10.5 bit pipeline adc的最前段,按理SHA至少11bit的精度,我不知道在哪里欠缺考虑。请指教!

把脉冲加宽,看看是不是几乎连续的,很有可能noise就这样,当然也可能是采样的DC建立对trannoise计算的影响

按理说sample 阶段的noise比hold 阶段小,不过hold 阶段有增益

你现在看的是单端的noise,建议看一下差分输出的Noise

说不准是个common mode noise, 也就是在你sample 时候下极板的那个中间电平的noise

应该不是,我完全把这个3个反相器级联的运放剥离出伪差分结构,做成一个single end的,结果hold的阶段还是在跳。

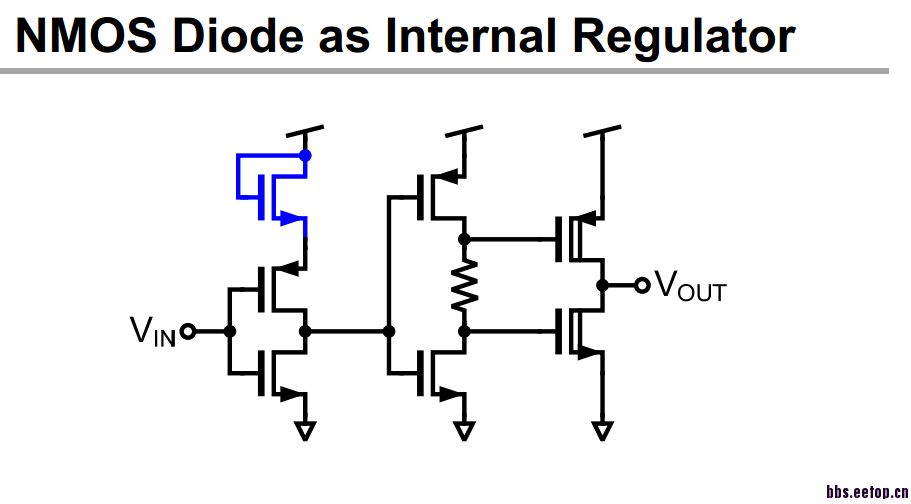

这个电路看起来有点怪,好像电路在共模处理上有点问题。

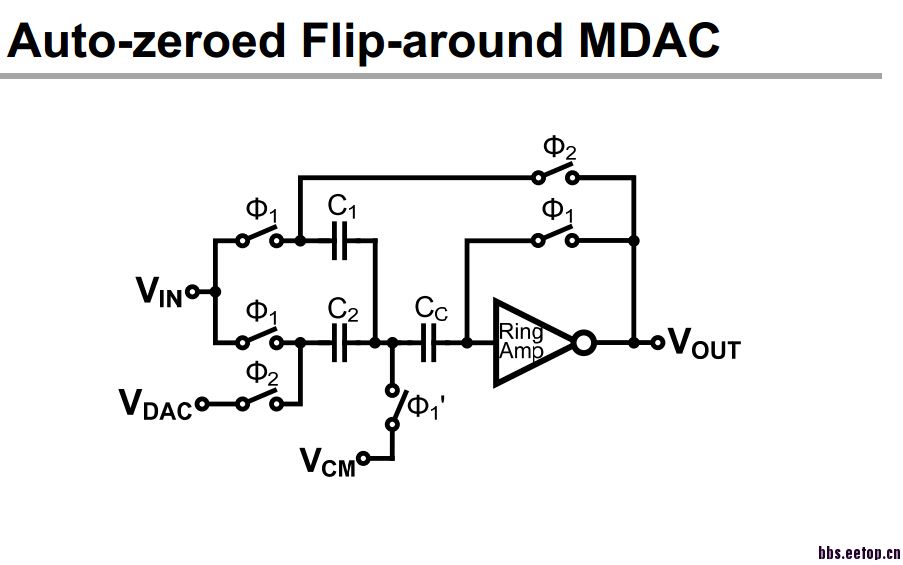

auto zeroing 会不会有这样的影响? 用了 auto zeroing的

这个电路最后是用两个单端组成一个伪差分了啦,见图,但是没有共模反馈,其中一个单端的应该也能正常工作才是。

auto zeroing 呢?

switch 的 MOS 的 inversion layer 的 charge 會向兩邊跑.也會透過 Cgs 把 gate 訊號 couple 到 Source/Drain.最好用 dummy switch 來吸收這些 charge.

用互补型的开关了,尽管charge injection 无法避免

感觉瞬态噪声仿真不太靠谱啊。

0000000000000

直接写email问作者。

你对这个ring amp 怎么看?

具体可以深入研究

我看是一个正常现象。由于有瞬态noise,运放输入端的电压是不断在变化的,最后输出的电压当然也在变化

thank you

加入的是transient noise?