求助Regulator的环路频率补偿

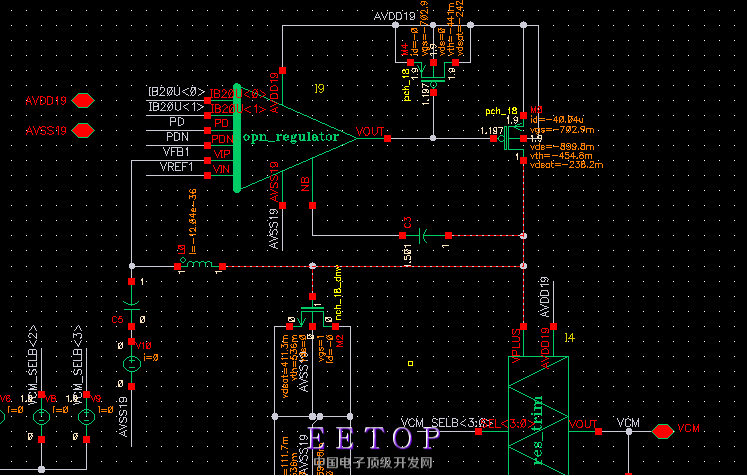

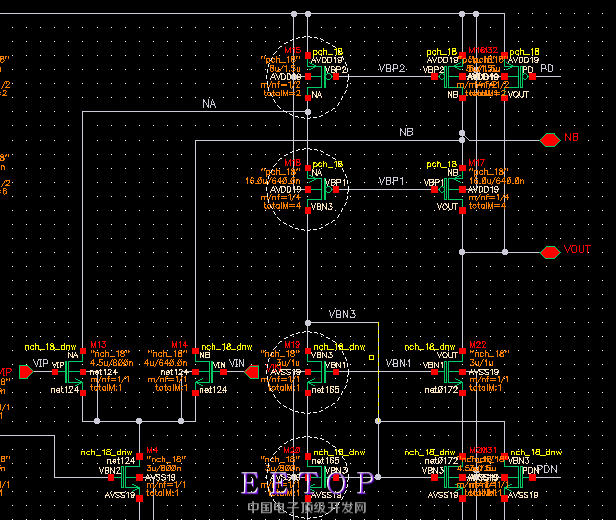

Regulator环路结构

仿真图如下

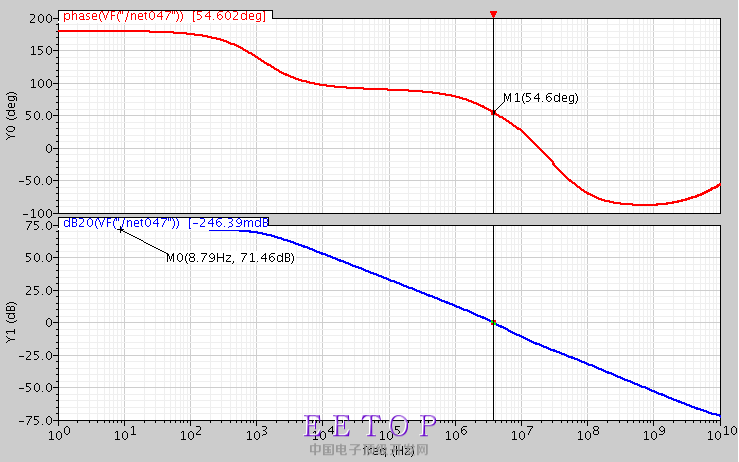

增加运放输出点电容后仿真图

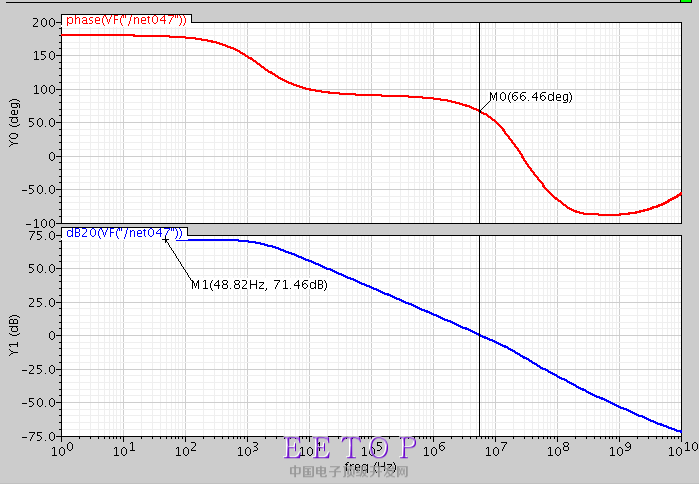

仿真波特图

仿真图说明是反的哈,第二幅是加电容之后的

与问题无关,我觉得这种弥勒电容的加法不能产生左零点吧,只是把零点往高频推了,因为前馈通路还在啊

可以的,详细推导请看拉扎维书P305页。

p305页并不是左零点啊,是高频处的右零点

是不是你的补偿电容相对与pass device的栅电容很小,导致你的主机点位置的电容增加时,主极点电容通过补偿电容对次极点电容有很大的影响

我的补偿电容用的金属mom电容,容值已经不小了,加的是2pF。

P管多大?drive的load current多大?

vout=1v? 直接feedback回来了?

1. 要增加output PMOS gain, 假設W/L不變的情況, 應該是減少電流才對 (想想 gm*ro 跟 i 的關係) ; 若是電流不變下, 則是調大L

2. 從圖上看來, 在gain=0的位置應該不只一個pole, 也就是你的OP裡有個3rd. pole跟你想的2nd. pole很近, 而加了電容之後跟著移動的是3rd. pole

不知道你的regulator是否需要提供電流? 如果只是產生個參考電壓補償就很簡單(pole不會隨load跑); 還有在OP out 放電容, 通常會放NMOS對地, 一來是考慮MOS電容跨壓vs.容值vs. layout size, 二來是power的noise通常比gnd大, 要看你的電路比較怕哪一邊的noise~PMOS的尺寸我取小了,使得第二级增益过小,我把电流提升到100u,尺寸取大后,稳定性的问题就解决了,但是PSR在高频下要20dB还在解决中

你的负载电容多大?2p的弥勒电容你是按照什么加的?继续加大弥勒电容或者增加功率MOS那一级的增益

问题就在于第二级PMOS的增益太低了,其实也做不了多高,所以使得密勒效应太弱了。

输入对管尺寸不一样?

只是把零点往高频推了,因为前馈通路还在