增益自举运放

时间:10-02

整理:3721RD

点击:

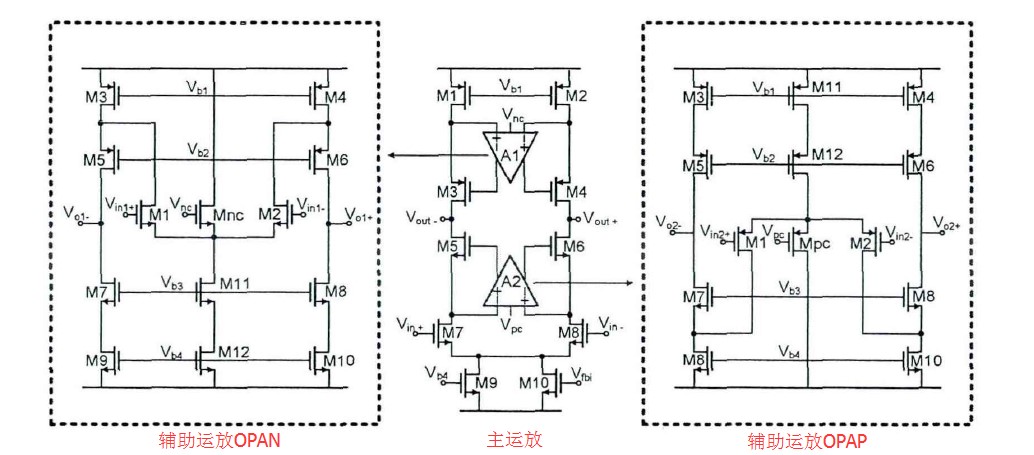

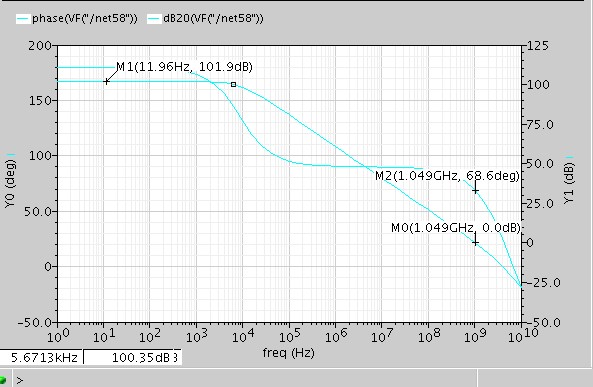

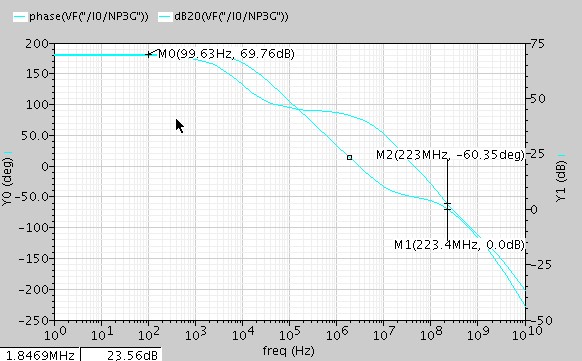

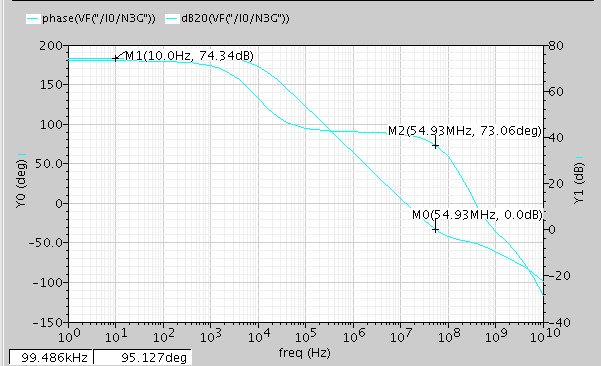

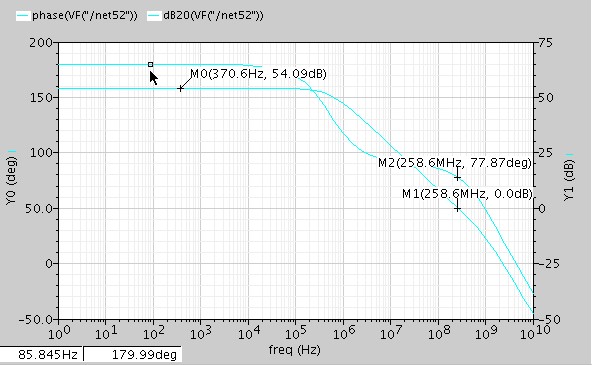

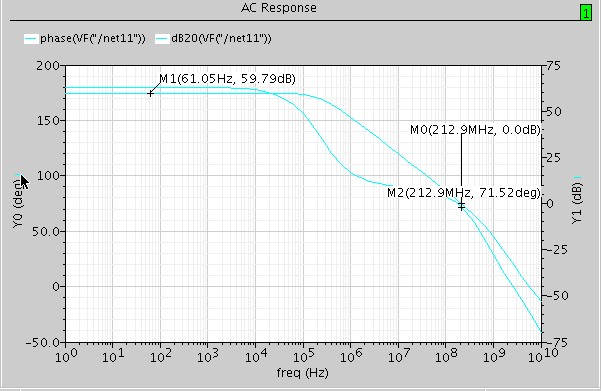

小白最近在做一个增益自举运放,关于辅助运放和增益自举后主运放的增益带宽问题还有的模糊,请论坛里的大牛们指点迷津,小弟感激不尽!运放的结构如图1所示,图2为主增益自举后主运放的波特图,图3为运放整体仿真时辅助运放OPAN的波特图,图4为运放整体仿真时辅助运放OPAP的波特图。我又将辅助运放OPAN和OPAP单独拿出来仿真,仿真时用的负载电容为500f(负载电容的选取是根据主运放中共源共栅管的栅电容确定的),仿真结果如图5、6所示。其中,图5为OPAN的波特图,图6为OPAP的波特图。

我想问的问题是

1、看到复旦的几篇博士论文和硕士论文中说为了避免辅助运放引入的零极点对对运放输出的影响,要求辅助运放的单位增益带宽要大于增益自举后运放的-3dB带宽,同时,也要小于增益自举后运放的次极点。但是有的论文却说辅助运放的单位增益带宽要大于增益自举前运放的-3dB带宽,小于增益自举后运放的次极点。辅助运放的GBW应该是大于增益自举前运放的-3dB带宽吧。?

2、当我整体仿真增益自举运放时,辅助运放OPAP、OPAN的增益和带宽相对于单独仿真时分别增加和减小了,关于这一点我的理解是辅助运放加到整体电路后,构成了一个负反馈,这样辅助运放的输出电阻增加,从而导致辅助运放的增益增大、带宽减少,不知我这样理解可对?

3、但我整体仿真增益自举运放时,刚开始增益自举运放的增益和带宽不太高大约分别为95dB、860M。当我在这个论坛里看到有有些朋友说要在辅助运放的输出接一个小电容后,我也在辅助运放的输出加上小电容(300f)仿真后,其增益带宽都增加了,分别为101.9dB、1.049G,为什么加上电容后增益和带宽都增加了呢?

图1

图1

图2

图3

图4

图5

图6

只是想说一句:注意offset注意corner变化,没了。

谢谢您的关注和解答!小弟愚昧,大神您可以解释的更清楚一点吗?

1 复旦说的对

2 你说的对

3 网友说的对

请问一下,你还有没有增益自举运放的资料呢?我现在在设计辅助运放的时候,也想采用跟你提到的这个结构,但是不知道这个辅助运放的共模输出是怎么控制的呢?

图中Mnc和Mpc是什么作用

请问小编的电路有没有参考资料?方不方便共享一下?谢谢!

你的带宽不是由主运放决定的吗?怎么会辅助运放的负载增加,你的带宽变化了