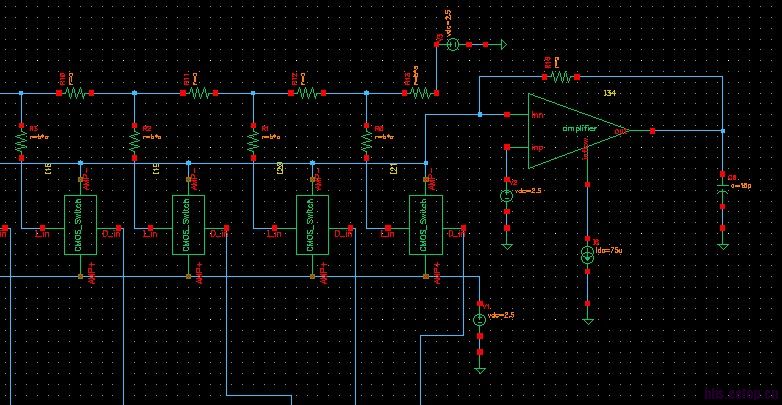

我设计的一个DAC

你的op-amp什么结构的?可能超出op-amp的共模范围了

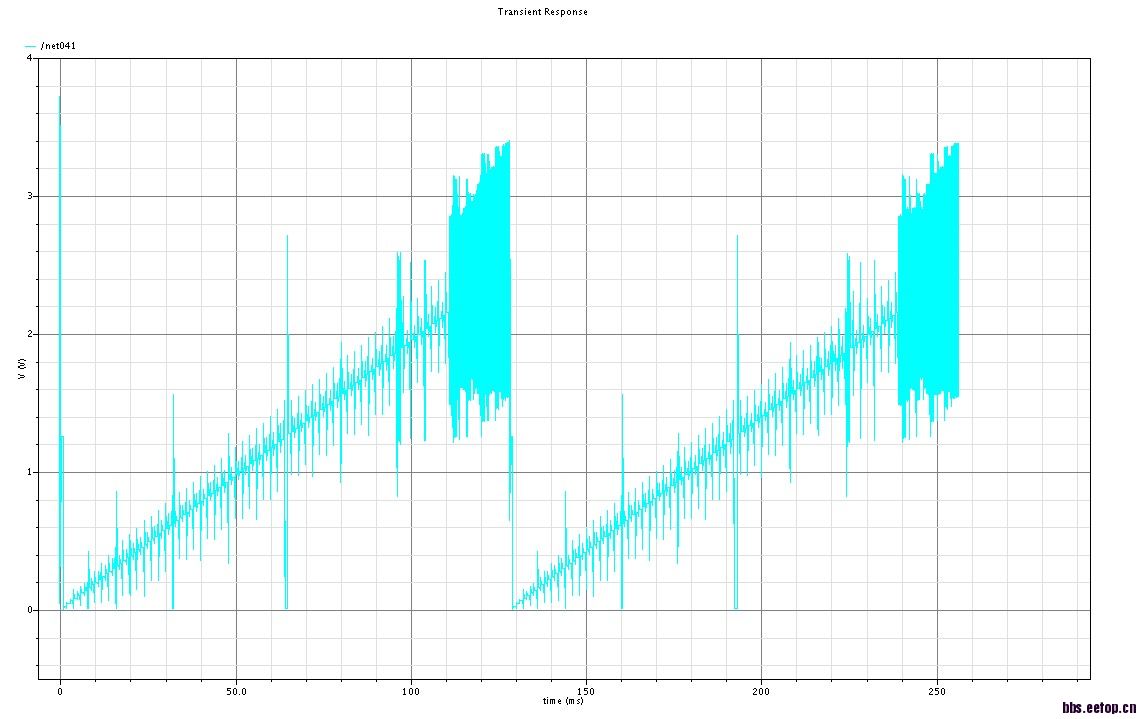

你好!我运放开始是用的pmos对作为差分对的折叠型共源共栅。后来改成了nmos作为差分对的。但是不管是哪种,都发生了严重的振荡,请问我应该怎么修改。

输入共模范围有问题?

从你的管子尺寸猜过去应该是0.35um工艺吧,那就是3.3v供电。

9.7mv-2.5v,这个范围很大,得用rail-to-rail的运放结构了,单个nmos或pmos输入管都无法工作在这么大的电压范围内

看过phase margin了吗,opa的输出load 是10p cap,内部有miller compensation,相位应该不够吧

可以看看环路稳定性

我用的是0.5um工艺,然后是5v供电。因为本来R-2R结构,放大器反相端接反馈,正向端接地,但是DAC输出是负的电压。所以改成正向端接2.5v电压,然后R-2R结构再做些改变。使得DAC输出变为9.7mv--2.5v.因为我还没想出输出0-5v的电阻比例的DAC方案。现在我的理解是,由于引入了负反馈,我的放大器的两个输入端应该一直都是2.5v的电压。所以我认为没有超过共模范围,不知道这样理解是否正确。

要改成rail-to-rail吗?我试试看。

你好!这个相位补偿的我全是凭感觉做的,而且这个相位问题我都回避。因为我做的这个DAC的负载要求是10p.能告诉我如果相位不够会影响哪方面的性能?稳定性?如何调整?你是如何知道不够的?我现在去做一下幅度和相位仿真看看。

250MHz, Rail-to-Rail I/O, CMOS

OPERATIONAL AMPLIFIERSTI 這篇OP的電流如何給還有VDD=2.5~5怎設計出偏壓電路

偶發帖在店員設計媒人禮希望各位前輩能教導小弟

thanks