关于SAR ADC 全电容结构的问题,大神求教啊

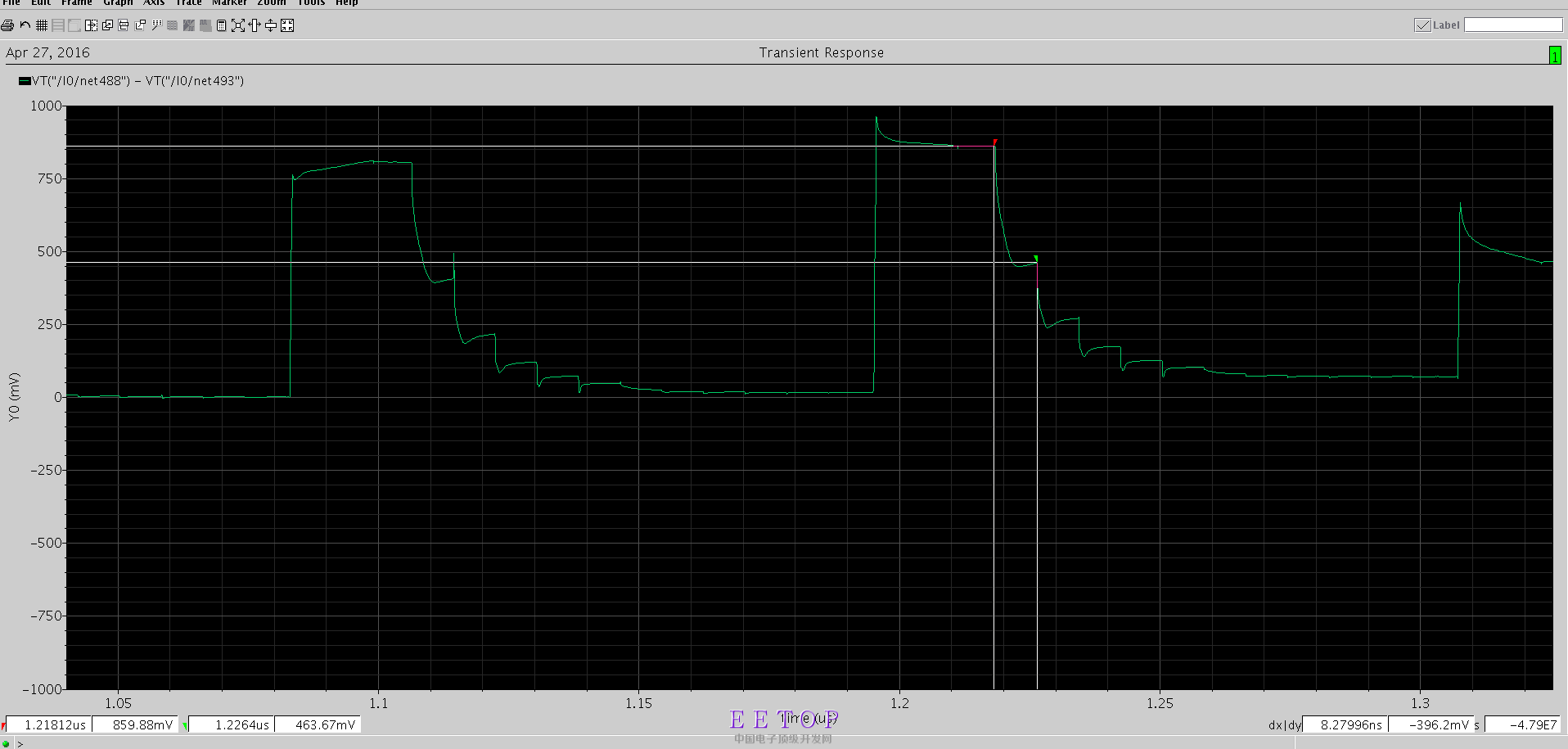

全电容结构,但是发现精度很低很低,下面给出采保电路的结果,请教大家,问题出在哪啊可能,谢谢了

全电容结构,但是发现精度很低很低,下面给出采保电路的结果,请教大家,问题出在哪啊可能,谢谢了

没有人帮一下吗

CMOS Switch R too bing 導致 settling time too long

把 PMOS/NMOS Width 變大!

Length use minimum Length.

一定要用bootstrapped sampling switch,

x线性度要看,很重要。

我已经把采保电路那个管子调到w=75u,l=180n了,性能依然没有改变

不带运放的栅压自举开关saradc,优势就在与低功耗,如果用到运放,功耗就高了

還是使用bootstrapped sampling switch吧!

你把采样开关用理想开关代替仿真一下,看有没有这个问题,就可以排除这里了。

比较器没正常工作吧,另外建立时间没给够的样子

这个开关我看过了,好像容易失真,功耗还很大

我今天还问别人,有没有理想的采保电路,有吗,这东西,用eriloga编写吗

我也觉得是没有正常工作,你看没看过这篇论文:A Low-Power 10-bit 50-MS/s SAR ADC Using a Parasitic-Compensated Split-Capacitor DAC他用的是近似计算吗,电容结构。我做成12位的,为何性能如此差劲

m4和m5是什么作用,感觉像是反相器,但是又不是啊,5的源没有恒接地啊

google:

Design for Reliability of Low-voltage Switched-capacitor Circuits

Page 55

Andrew Masami Abo

Bootstrapped switch 只消耗動態功耗,沒有靜態功耗,應該是很省電的耶!

analoglib里面就有啊。

learing !

关于SAR ADC 全电容结构的问题