AMS仿真结果不正确

时间:10-02

整理:3721RD

点击:

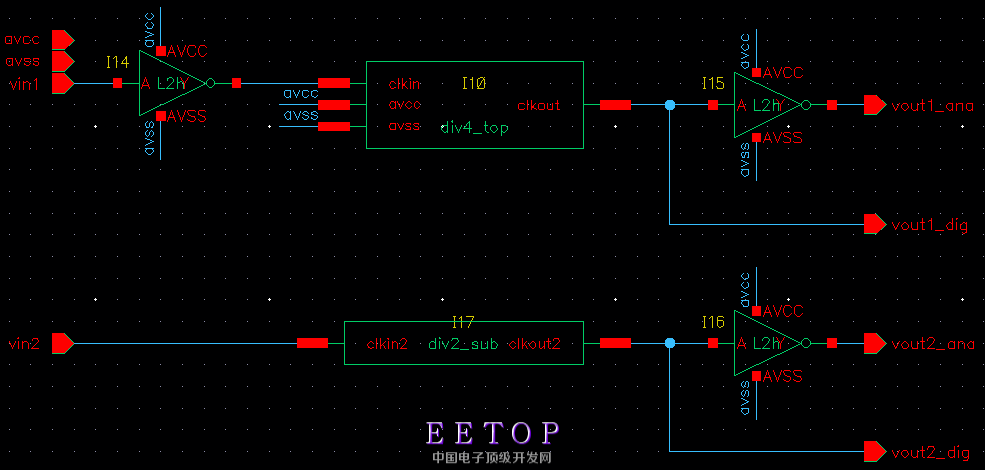

1. 搭建如下电路:

2. div4_top电路如下:

3. div2_sub代码如下:

// Created by ihdl

module div2_sub (clkin2, clkout2);

output clkout2;

input clkin2;

reg clkout2;

integer i;

initial

begin

clkout2=0;

i=0;

end

always @( posedge clkin2)

begin

if (i==0)

clkout2 = 1;

else

clkout2 = 0;

i=i+1;

if (i==2)i=0;

end

endmodule

4. 错误描述如下:

4.1 添加div2_sub数字单元(第一幅图下)后,仿真结果不正确,各结点均有波形;

4.2 删除div2_sub数字单元(第一幅图下)后,第一幅图上,仿真结果正确;

4.3 为什么仅仅添加div2_sub后结果就不正确了呢?难道AMS仿真时内部不能有两个数字模块?

2. div4_top电路如下:

3. div2_sub代码如下:

// Created by ihdl

module div2_sub (clkin2, clkout2);

output clkout2;

input clkin2;

reg clkout2;

integer i;

initial

begin

clkout2=0;

i=0;

end

always @( posedge clkin2)

begin

if (i==0)

clkout2 = 1;

else

clkout2 = 0;

i=i+1;

if (i==2)i=0;

end

endmodule

4. 错误描述如下:

4.1 添加div2_sub数字单元(第一幅图下)后,仿真结果不正确,各结点均有波形;

4.2 删除div2_sub数字单元(第一幅图下)后,第一幅图上,仿真结果正确;

4.3 为什么仅仅添加div2_sub后结果就不正确了呢?难道AMS仿真时内部不能有两个数字模块?

div2_sub是2分频电路吗?

如果是的话,

把always改一下

always @( posedge clkin2)

begin

if (i==0) begin

clkout2 <= 1;

i <= 1;

end

else begin

clkout2 <= 0;

i<= 0;

end

end

是二分频,code没问题。问题已解决,谢谢