奇怪的芯片问题

不知道大家有没有遇到过这样的问题:

芯片晶圆测试的时候,良率不错,FUSE之后的基准、偏置电流、时钟等等都在设计范围之内。但是用示波器观察的时候,发现基准电压上面都叠加了一个非常不规则的高频噪声,同时时钟非常不稳定,波形和抖频的时钟波形一样(设计是没有抖频的)。

把CP测试OK的晶圆封装成成品后,FT测试时控制时钟的波动范围在-/+1KHz内,良率瞬间降到10%。

现在找不到原因,郁闷死了。

内部5V电源产生电路

TRAN波形

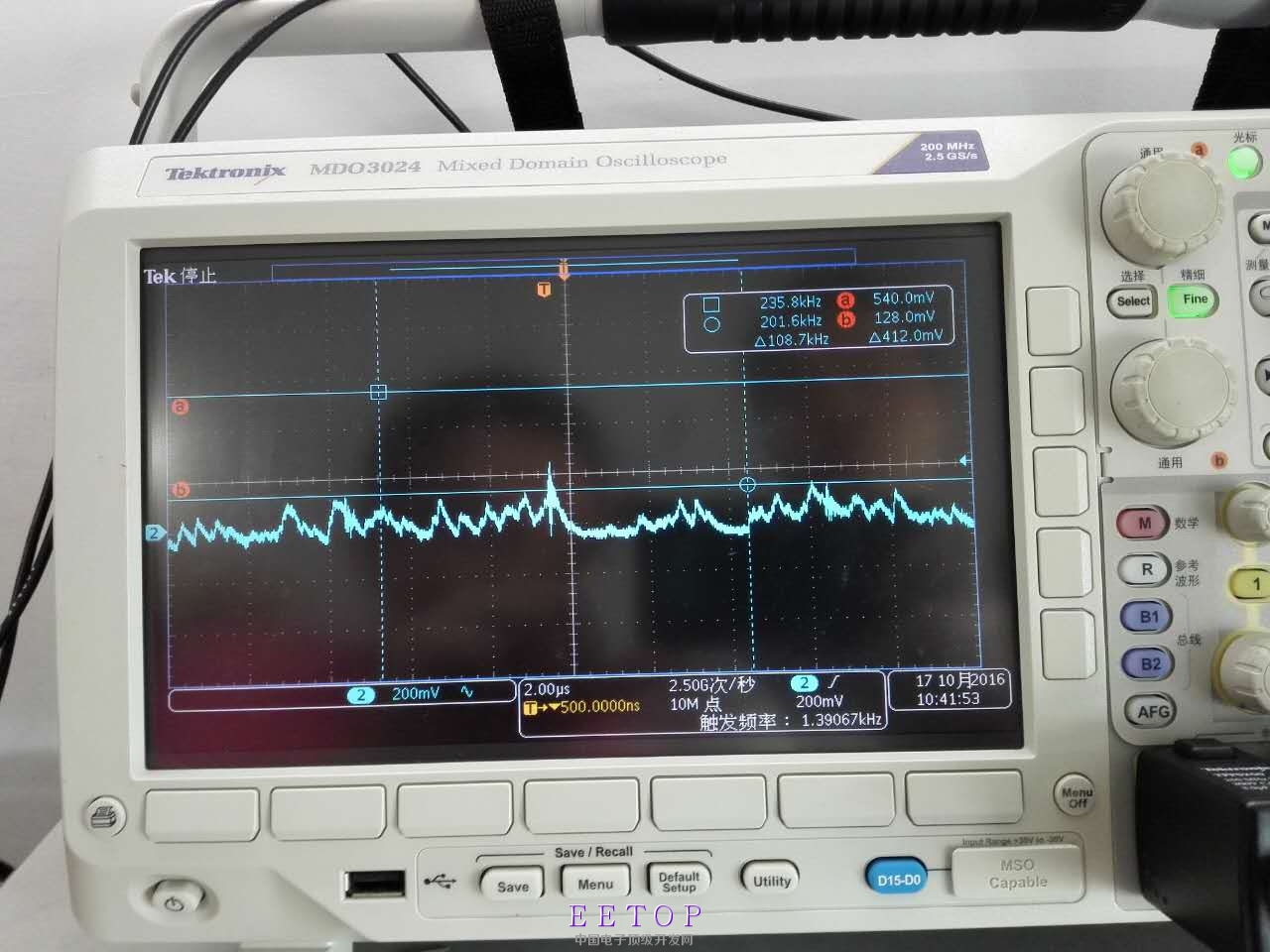

AC波形

你的基准,偏置电流,时钟都做了fuse trimming吗?如果你不做fuse trimming,FT测试和CP测试有区别吗?

trimming一般情况下应该只有部分需要trimming。有一部分应该本来就可以的。

而且一般都有个控制位,trimming是否有效,你可以寄存器或者什么控制的。

感觉像是你的trimming控制逻辑在时钟作用下乱来。

测试模式最好不要让power管switching,噪声很大的。

估计不是电路内部的问题。示波器观察时,你的探头阻抗是不是匹配?接地是不是良好?如果可以,给个你们测试的原理图和照片,以及测试条件的描述。示波器的应用不比电路设计简单多少,真的。

封装后,由于存在封装应力问题,会有一定的参数漂移。良率下降这么多,无非两个原因:你们的时钟robust不够,你们找的封装厂太烂了。

祝你好夢!

CP时候拉多大电流测,实际又是拉多大电流测,可能正常工作的时候开关动作已经严重干扰了电路工作

看看先

layout的时候有充分考虑噪声影响吗,例如VINA VINP,VSS,VSSP分开bond,

这是3A的buck吧?集成大电流功率管对衬底引入噪声不奇怪的

其实如果不看波形的话,CP测试和FT测试良率都不错。如果看瞬态波形的话,瞬间崩溃。这个芯片用在反激变换器上面,如果频率这个样子的话,相当于很大的抖频,用在没有浸油的变压器上面,就有嗡嗡的响声。

其他参数都OK。悲剧。

BUCK 3A的时钟很稳定。反到是这个SSR的反激控制芯片时钟很不稳定,把基准电压和内部5V电源拉出来看,叠加的高频噪声是一样的。两者的电路结构其实大致是一样的。

把DRIVER部分关闭和不关闭,都是有不稳定的噪声出现。现在一直在找,改了几次版了,都没有改好。

嗯,FT和CP的测试机抓出来的值经过FUSE之后都在设计范围之内的。但是就是良品拿回来测,就会出现噪声,基准和频率都有噪声。然后返回确认测试CP和FT结果,发现CP和FT有同样的问题,只不过是没有发现。

你的基准电路会不会有不稳定的问题呢?仿真确认没有?

看你电路好像有高压的管子,这里输入电压在范围内变化结果会怎么样?另外,你尽量简化,先只测试基准,buck这些都关掉静态下,确定基准是否干净。

感觉你的问题是基准有抖动,在封装压力下,抖动更厉害?

基准是有抖动,但是我们通过FIB、改版调整PM都无法消除高频噪声,最后发现是基准的噪声和内部5V电源的噪声是一致的,但是5V的噪声源一直都没有确认到哪里产生的。

有高频噪声(用测试机测试直流电压是看不出区别的)

没有高频噪声(就是在FT中剔除噪声干扰,剩下的10%的良品)

Zenner在上华工艺中不能正偏 ,这估计是这个电路的死穴所在.

做FIB尝试把正偏的Zenner短路,估计VCC就没有这个噪声了.

内部5V的电压是如何产生的, cp未trim的芯片也发现这个问题吗?

牛人啊,一看就知道是上华的工艺,这个工艺的确是上华1um40v的。不过zener不能正向使用,有什么说法么?能解释一下么。

5V的电压见一楼,我贴上去了。CP的时候发现不了,因为测试机抓出来的数据都不错,频率是计算的平均值。

一般可以正偏使用的Zener属于FloatingZener,有NBL层,并做高电压偏置.

如果没有NBL层,正偏Zener和pusb之间就形成一个寄生pnp,抗噪声能力就非常弱.而且正偏电流也有要求,通常小于1mA.

上华工艺即时实现Floating Zener的结构,但是给客户两端模型,建模很粗糙,极其容易造成设计者的错误判断和使用.通常国外工艺的Zener都是三端器件,可以仿真出漏电流的大小.

如果搂住做实验把这个Zener断开,估计VCC上就看不到这个噪声了.需要使用NPN CB短接正偏使用,以替代Zener.

上华工艺想玩得好,需要自己对器件的理解能力很强才行,这也是烧钱烧出来的经验.

你可以做FIB把那个正偏的Zener断开,VCC只小一个Vz值,看看还有噪声干扰不?

嗯,正准备试试。已经改了三次版了,均没有办法解决此问题啊。

这是非常成熟的电路结构.只是可能参考了别人家的电路吧,比如一些SOi工艺,Zener就可以正偏.

这个建议价值连城,小编该拿些诚意出来了吧

嗯,反向的电路,以前用过其他工艺没有出过问题的。上次同样类型的芯片,我自己换了个LDO的结构,也没有出问题。现在用上华的另外一个BCD工艺,zener的pdk也是两端的,同样的电路,也没有出问题,而且性能杠杠的。

没有想到就这个出问题了。

小编说,想要什么,只要有的,我都可以给

也不完全是这样吧

是的,我理解有限。不过小编的问题看样子是本身的设计问题,只是cp的时候没有发现。