请教sar adc中的比较器

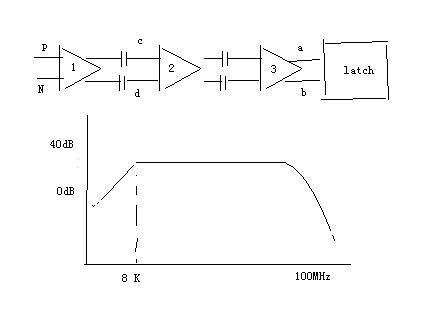

hspice 仿真发现,在低频 8k左右位置出现一个未抵消的极点。 求高人解答~

怎么测的得到这个的不对的结果

是capacitor coupling

低频的时候是个 high-pass, 当然是这样了

capacitor coupling ,中间这个失调消除电容的问题吧? 能具体一点吗?

其实从第二级输入端看 对输入P,N的增益就有这个衰减了。这个东西怎么消除或减小?

从以前其他工艺的仿真来看,没有这个现象。

第一级跟第二级之间已经是AC coupling 了,high pass corner depends on cap 和output impedace of 1st stage.

更新了下问题描述。

1. 1,2级之间ac coupling 没错。

2. 对c点,低频处出现高通, 而高通应该是电容,电阻。 而非你说的1st 输出电阻 + 电容 。

3. 对c点而言,考虑负载, c点往后看见下一级输入MOS的栅级,栅级对地电阻应该非常大。所以几百f电容加 Gohm级电阻,极点应该在1k不到或甚至几Hz以下。

4,所以按楼上的说法,跟输出电阻有关的话,又是什么关系呢? 你能讲清楚一点吗,不要太笼统。 方便计算,假设第一级增益为10好了, 输入mos管的gm=300uA/VRout=100K/3好了 ,coupling电容算100f好了。 能大概算一下吗?

赫赫,咋没有讨论了,期待中

谢谢小编的分享了!

低频是这样?不太对

学习一下

关注中

cap 隔离直流应该是有个条件的,两端都有dc放电通路,如果一侧是悬空,那么,应该是增益为1,如果要是考虑输入栅极电容,那么2rd的输入应该是两个电容的分压,这个传输函数貌似没有所谓的频率响应吧?应该是两个电容之比吧?这样子的话,你仿真图还是有问题,你仿真的时候你的静态怎么给?毕竟栅极输入没有DC通路

thank you

第二级输入没有正确偏置

kankan louzhu a

thnak you

learing !

想问一下,你的这个问题解决了吗?可以清楚的知道是什么原因引起的吗?

请教sar adc中的比较器