12B125M HS-SAR ADC in 28nm 的一点测试结果哈~

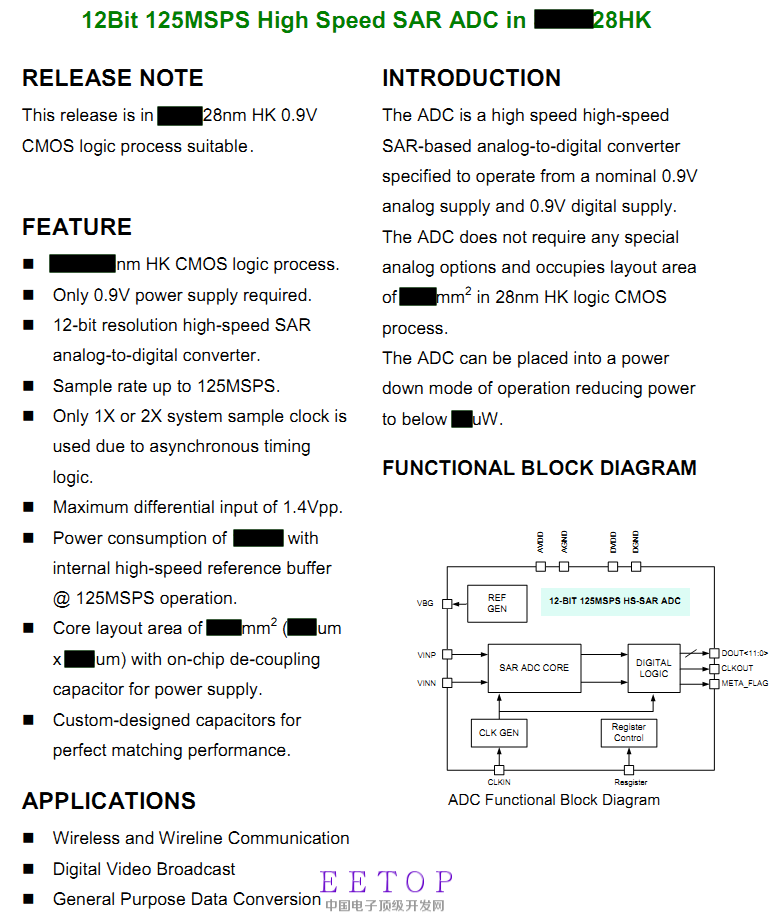

前段时间忙活的一款28nmHK(国内foundry~)工艺的12bit 125MSPSSAR ADC片子到手了,测试结果看上去和预期设计目标基本吻合,性能结果和paper里那些SAR ADC没办法用相同的评价标准去衡量,但是作为一款真正可以非常便捷、低成本地集成于SoC中的商用化ADC IP,这个测试结果也算不辱使命了哈。PS: 因为还没有正式release,所以暂时遮挡了部分参数,其实也没啥值得保密的哈哈,大家凑合着瞅瞅就好啦

牛啊,加了input buffer 了么?

功耗不透露啊。有enob vs. fsig 的图么? fsig 到40MHz 怎么样?要不好像pk 不了同类型的sigma-delta.

挺好的,reference是完全片内的,没有拿到pin上?

电容阵列是binary 还是什么? 最小单位采样电容多少,2fF?

因为只有0.9V单电源供电,这个是不带全集成输入驱动器的,为了保证足够的线性度和信号幅度输入驱动器就得上1.8V供电的source follower了。考虑到实际应用中前端驱动器的驱动能力的问题,因此设计了25%和50%周期作为采样时间的可选择配置。另外,根据应用场景的不同,设计了A和B两个版本,一个版本是全集成bandgap和high speed reference buffer的,功耗小于8mW(5.8mW);一个版本是直接利用电源和地作为参考的(需要做良好的on-chip decap和damping compensation),功耗小于2.5mW(2mW)。

高频输入主要依赖于时钟的质量,这里时钟电路比较纯粹,输入信号频率60MHz时也没啥问题哈。

全集成的方案,集成时只要需要一对电源/地管脚(VDD/GND)、一对差分输入管脚(VINP/VINN)和一个可选择的测试管脚(VBG),因为是场景不定地商用化IP,所以整体结构里全部采用静态逻辑单元,没有采用任何的动态逻辑单元(尽管动态逻辑单元功耗更低、速度更快,但是低速模式时容易漏电和PSR差),保证1MSPS到125MSPS、-40c~125c、供电波动等条件下都能稳定可靠的工作。

用了lvt 器件没?要不slow -40C, 跑125MHz 加上reduced radix 很吃力吧?SOC 环境能找到给adc 的专用电源地管脚?貌似带ref buffer 的比较合理。

全集成的基准方案和直接用电源/地做基准的方案都有厂商采用,S3他们家就比较喜欢全集成的基准方案,syno....他们家就比较喜欢直接用电源/地做基准,各有优缺点,也还是视应用场景而定谁更合适了~

同问!

多谢

个人创业?看来小编资金雄厚啊,顶你一下,祝早日发大财。

部分结构上用了LVT,要不Vth确实比较高,要不一些极端PVT情况下,真的会悲剧~

哈,俺就是个在公司下苦力干活的哈,估计就只能指着买个彩票发财了哈哈哈哈

赞拉风哥,0.9的电压,速度还能这么快

同问?多谢

The buffer might consumes more power than the adc I guess. But well done sumig!

从匹配度上来讲4fF~5fF左右就够了,为了保证采样相的KT/C,单位电容又适当放大了点;分段电容加误差冗余补偿,但是多出来的冗余位转换是使得比较器占用的转换时间更多了,所以如果单纯的追求极致的转换速度的话,还是标准的二进制比较合适,但是这个时候就需要想办法解决基准电压建立的问题,比如动态电荷补偿技术。

是啊,这个也是一直比较头疼的问题,因为需要最小的面积,因此片内加大面积decap的方式是行不通的,所有只能做宽带reference buffer,这部分buffer功耗占了差不多75%以上,以后抽空升级几个动态电荷补偿技术的版本试试。

我记得冗余只有当时间常数RC到一定大小时才会有速度优势,单位电容小,rc本来就小,所以额外的周期可能反而多了时间。不过冗余还是能够校正reference的波动吧,也就是可以降低对reference buffer 的设计要求。不知道这么理解对不对。

是这个样子的哈,开关RC基本不是问题,主要还是reference settling的问题哈哈

咋做动态补偿啊?

Fom值不太好

哈,Fom确实没办法和paper着重追求这些指标进行比较哈,为了Fom的,当然可以上动态逻辑单元(功耗低速度还快),片内狂加decap,降低reference功耗,不过这个从商用化角度讲不太现实。作为商用化IP,主要还是以如何以最低使用成本和最小风险满足各种客户的不同集成需求作为首要目标,不过以后抽空还得做升级版本之类的肯定是砍功耗和面积了,客户一个个确实巴不得ADC零功耗、零面积才满心满意哈哈哈。

就是用个额外电容预充电荷,然后根据每次转换进行相应的电荷补偿。

有paper么?

貌似,还真没注意有啥好的文章可以参考,zero-crossing PIP ADC里用过类似的方式,但是那个补偿的是大信号,不够精确,SAR ADC也只是思考过,没正儿八经的搞哈。

哈哈,你可以去弄个isscc paper

哈哈,搞不了了,还是老实看isscc吧哈哈哈

搜今年的esscirc

同意这点。

另有个疑问:如果输入端口阻抗很高,是不是需要做片内input buffer?这样R2R buffer在片内好做么?

是这篇:A 1.6 GS/s 3.17 mW 6-b Passive Pipelined Binary-Search ADC with Memory Effect Canceller and Reference Voltage Calibration?

挺好的,有没有INL曲线可以看看?谱上有很多Non-harmonic spur