LDO设计时PMOS调整管的宽长比怎么定

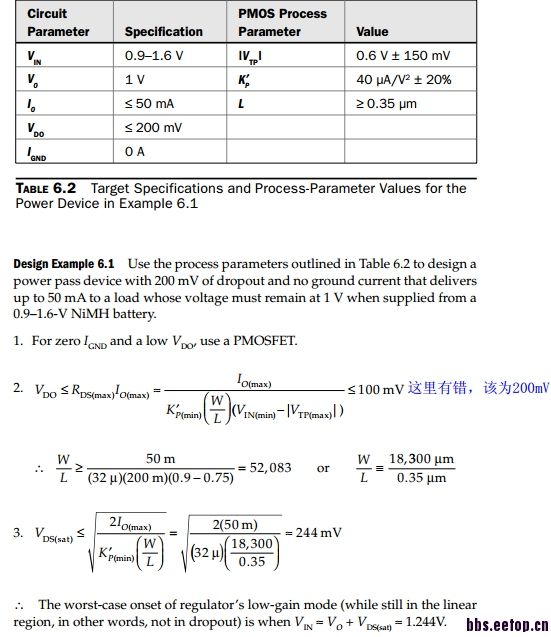

看了mora的LDO那本书,如下图所示(英文电子档-p236),但是没明白他的计算是基于什么考虑。

他的意思是当输入电压很低时,电流最大时,PMOS工作在线性区(而且从公式来看是深线性)?通过这个假设计算得到一个宽长比?

输入电压最低时,压差最小,让管子工作在线性区且满足最大输出电流,也就是使PMOS功率管栅极电压摆到最低的电压值(受前级电路限制),此时计算出的管子的宽长比和面积都是最小且满足电路工作要求的。输入电压变大时,管子只会更易驱动且可能进入饱和区

谢谢!比如下面这个LDO结构,考虑前级的话,就是Vn2_min=2*Vov+Vgs(Vgs为M21的)?还是Vn2_min=Vgs(即认为M3、M7压降为0)?

保证M3、M7管子饱和工作,且M21的Vsg够用,即Vn2_min=2*Vov+Vsg,这只是理论的计算,还需要通过仿真来逐步调整。另外,此电路的话大电流时主极点设置在内部,还要考虑补偿电容Cc受功率管增益形成的米勒补偿效果来调整尺寸,还有就是考虑功率管本身的面积、寄生电容等等,说的有点多了。

“另外,此电路的话大电流时主极点设置在内部,还要考虑补偿电容Cc受功率管增益形成的米勒补偿效果来调整尺寸,还有就是考虑功率管本身的面积、寄生电容等等”

非常感谢您的指点!我是菜鸟,所以您说的越多越好!

这是个大电流LDO-200mA,文章作者推导的传输函数(如下)我没看出来主极点是在内部还是外部?

另外,“还要考虑补偿电容Cc受功率管增益形成的米勒补偿效果来调整尺寸”这怎么理解?

输出大电流时,Roeq变得很小,Roeq*CL会远小于gmp*Roeq*ro1*Cc(但gmp*Roeq随电流变化不太大,就是米勒补偿乘积项),也就是主极点在内部吧。如果在输出大的电流不变的情况下,米勒乘积项还是偏小,就需要增大功率管尺寸以提高gmp*Roeq,或者增大Cc,或者增大ro1,而且管子一旦进入线性区的话,乘积项gmp*Roeq本身就会减小,可能需要作出调整。

听了你的讲解略懂了一些, 结合仿真来看,就像你说的那样---还得根据满载时对Cc放大倍数的要求来调节功率管的宽长比

请问 dropout如何设计的呢?如果vin=5V,range=4V~6V,Vout=3V,那么dropout=1V?还是多少?

如果vin=5V,range=4V~6V,Vout=3V,Iomax=10mA,应如何设计power mos的尺寸呢?

按您的题设条件,最小的dropout电压就是1V,也就是Vin=4V时的值。LDO一般要保证Vin最小时电路要能正常工作,因为此时功率管最易于进入线性区从而导致电路性能下降,Vin增大后功率管越不易于脱离饱和区从而性能不会出现下降。最小Vin时让PMOS功率管工作在线性区或线性区边缘,既可以充分利用其栅极向下的最大摆幅(受前级电路所限制),也能最大地减小功率管尺寸,不足就是与功率管增益有关的性能会有一定的下降,这时就是通过设计来满足最低的相关性能指标即可,从而平衡功率管尺寸与电路性能了

你的range指的是什么?

input range,就是正常Vin=5V,设计时考虑Vin range 4--6V,这样有问题吗?哎呀,如果这个ldo由内部的ldo5(5V)供电,对ldo5要求又高了

直接写vin range 4~6V 不就行了。LDO的Vin肯定看Vin,min,更高的没太大意义。

昨天想了一下ldo应该看dropout,也就是最小能够稳压的Vin值,dropout越小,效率越高。

所以,一般设计为200mV?

也就是PMOS的D 端和S端最小压差为200mV,我用这个最小Vds值,按照平方律公式初步计算W/L值。

这样有问题吗?觉得哪里好像不通。

而且书上说dropout=Ron*I,为什么呢?

可以理解为dropout为POWER MOS最小的过驱电压吗?

昨天想了一下ldo应该看dropout,也就是最小能够稳压的Vin值,不应该看Vin range,dropout越小,效率越高。

所以,一般设计为200mV?

也就是PMOS的D 端和S端最小压差为200mV,我用这个最小Vds值,按照平方律公式初步计算W/L值。

这样有问题吗?觉得哪里好像不通。

而且书上说dropout=Ron*I,为什么呢?

可以理解为dropout为POWER MOS最小的过驱电压吗?

drop不等于Ron×I那等于什么啊!?不就是一个串联电路么……

而且mora的这个例子,Vin range=0.9V~1.6V Vout=1V, 最小的Vin=0.9V<Vout=1V,这样可以吗 ?

还是公式中应该按照Vin,min=Vout+dropout?

0.9V的vin Vout=1V,那是dc-dc,尽信书不如无书,自己甄别。

最小压差Vdo时按照平方律计算的管子尺寸,前提是PMOS功率管是饱和工作的,也就是此时需保证栅极驱动电压Vg>Vinmin-Vthp(正)-Vdo也即Vsg,max=Vinmin-Vg<Vthp+Vdo。对于前级为一般的cascode误差放大器加上PMOS源跟随器形式的缓冲器结构来说Vg最低可以向下摆到Vg=2Vdsat,n+Vsg,p的电压(适合最小电源电压不是很低,比如Vinmin=3.5V),而对于前级为互补形式的缓冲器结构来讲Vg一般可以向下摆到Vg=Vdsat,n的电压(适合最小电源电压本身不高的场合,比如Vinmin=1.8V),假设Vdo=0.2V,Vthp=0.8V,Vdsat,n=0.2V,Vsg,p=1V,你可以分别估算一下两种场合下饱和工作时的Vg值与Vg向下摆动的最低值,结果是很明显的。为了饱和工作,可能需要很大的功率管尺寸,而利用其向下最大摆动从而线性区工作的公式计算的话,同样输出电流值时功率管尺寸会小很多。另外,如楼上所述,LDO输入0.9V输出1V是不可能的,除非加了升压DCDC再接LDO。

恩 谢谢 我的确有尽信书的毛病,自己体会不够深刻

对于Vin,min=0.9V 的问题,麻烦你看一下首页的公式。我想说的是,对于LDO来说,线性电阻中是不是应该代入Vin,min=dropout+Vout ?

对于本例为0.2+1=1.2V,而不是0.9V呢?对于LDO来说。

当然,书上没说是LDO。

按照这个说法,就是要充分利用功率管栅极电压的摆幅下限来提供最大电流,但是mora书中计算功率管尺寸的时候直接写的Vin.min-Vtp.max啊,不应该是Vin.min-Vg.min-Vtp.max么? ps:Vg.min指功率管栅极电压的最小值

刚才翻了下那本书,是中文版177页的公式吧,公式没有错,那个例子是设计一个功率开关器件的尺寸而不是设计用于LDO的功率管的尺寸,因此Vg是可以摆到地也就是0V的,也即Vg.min=0。

嗯呢,就是小编贴的那张图,确实是设计功率管尺寸的。如何Vg可以摆到0V那就说得通了,谢谢大神的回复

学习学习

对 这个0.9V怎么来的,Vin=0.9V,Vo怎么等于1V?

学习学习

書上寫的0.9~1.6是Vin哦,可不是Vgs。這公式很奇怪,在線性區的Ron公式里也是(VGS-VTH)啊,怎麼搞出個(Vin-VTH)。

如果說書上的Vin是您講的VGS的話,那帶入公式的最小值也不會是0.9V啊。

還有第三個等式也沒看懂,VDS什麼時候和Ids有了這個關係式?

有人能解釋解釋嗎

Ron的等式明白了,Vg=0,Vgs=|Vg-Vin|=Vin.

第三個等式還是沒明白。正常公式里應該是Vgs而不是Vds啊。