ldo瞬时仿真震荡

上图为ldo的AC和tran仿真,仿真条件均为无电流和电容负载。

疑问是,为什么ac相位裕度满足条件,但是tran仿真en后却会一直震荡。

另外发问。ac仿真相位裕度够的条件下,就一定可以保证不震荡么。?

上图为电路原理图和AC仿真线路图,从AC_IN加AC源,观测N5点的波特图。

你先确定电路只有一个环路,若有多个环路保证各个环路都稳定。

是在空载情况下震荡吗?

AC仿真?开环仿真的?AC激励加哪里?

附图

是空载,但问题是我AC和tran仿真是在电路在统一的负载条件下进行的,疑惑是AC曲线没有问题,但是tran 会震荡。

图以附上,根据你说的,这个结构还真不只是一个环路,内部电流buffer也存在一个环路。这个小环路已经包含在我仿真的整个系统里面了。

难道小环路的不稳定最终不会体现在整体AC仿真中吗。》》?

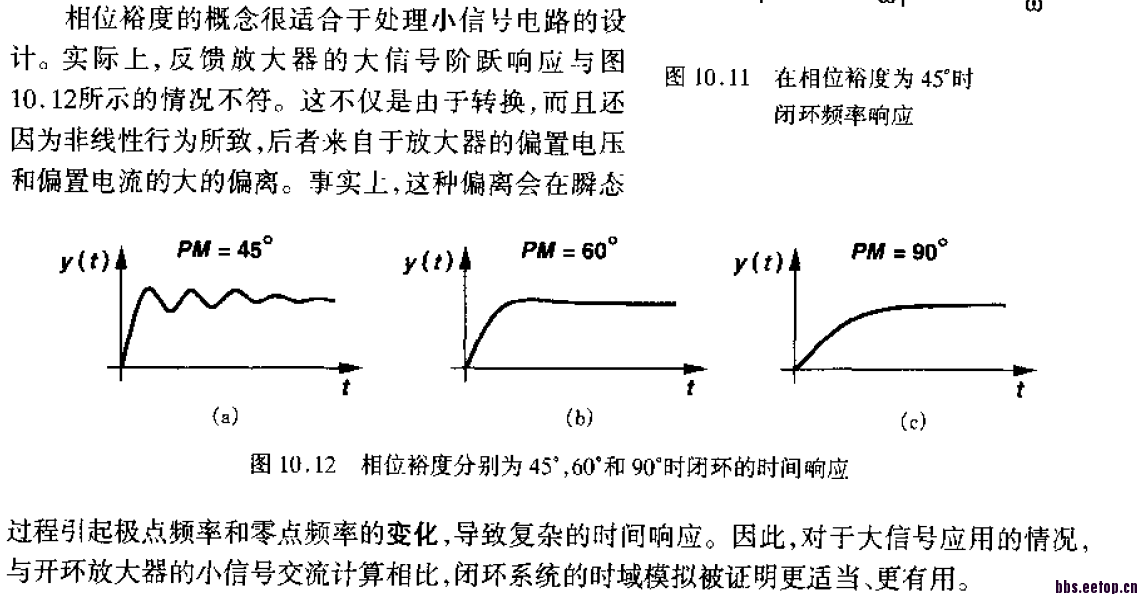

拉扎维上面的

你这个应该不是做产品,在实验室做还是自己搞着玩?你电流buffer要是也是随着负载变化,也要分不同负载确定小环路的稳定性。建议别搞这没实用性的东西,浪费时间。

这是一个很经典的电路,电路应该没有问题。

你确定你的DC工作点都对了吗?

如果你只是从paper上把circuit 弄过来然后仿真,是没有什么用处的,多分析分析,

你first stage 的gain, voltage buffer的pole,以及直流偏置是多少.

这个还真不是玩的东西。有paper而且市场里面也看到过实际的东西。

目前看下来好像是这样的,电路里面存在三个环路,我仿真的是一个主环路,还有一个电流buffer内部环路和补偿电容的一个环路。

内部buffer 环路没有问题,但是再一次仿补偿电容环路AC 的时候发现这个环路裕度不够,可能由于这个环路引起震荡到大信号非线性区,从而导致工作点的大幅度偏移,和AC仿真主环路产生矛盾。

初步看起来,系统主环路的相位域度保证并不代表系统内子环路的AC稳定。应该确保所有环路都满足稳定条件才可以保证系统的稳定。

那你花时间好好搞把,谁家产品用这个了?这个电路就像瓷娃娃。

是capless还是单片的LDO么?多大负载?

先确定DC工作点吧,然后AC才有意义。

现在capless的LDO都用这个方法。

capless的我没做过,一般capless是输出完全不带电容,还是带小电容?capless用这种结构是为了保证瞬态响应好还是其他原因?

会带几百pf的片内电路,然后把主极点坐在外部,

capless通常是把主极点做到内部。同时对负载电容有一定要求。

DC工作点已经确定,只是在由于反馈环路的不稳定,系统DC点呗反馈环路引起的震荡飘到另一个DC点上了。目前看下来好像是这个样子。

从文献上来看这个电路的好处是no loading 到 full loading稳定工作,内部电流随负载电流自动调节,节省功耗,在一个可以提高瞬态响应。

如果仅是因为这些原因,这个电路就太麻烦了,有其他方法功耗可以更低,电路可以更简单,一些性能也会更好比如dropout

也关心这个问题,能给一篇paper吗?

paper 上的东西一般都较复杂实用性低,但里面的思想很值得学习。没有相关paper。

没有仔细做过,不要轻易下结论!

这个电路是Ti写的paper,完全可以工作的!我用这个架构做了多个产品(有些结构简化了)卖出去N多了,只不过把其中的NPN用nmos代替了。

这个东西,包括paper给出的环路断开的地方,都是值得商榷的,所以一般AC仿真都会得到错误的结果。LZ在N1的节点,断开环路,再来仿真AC,就可以了!AC仿真和tran仿真可以精确对应起来。仿真震荡肯定是PM不够,前提是AC仿真本身要正确。

我没说这个不能工作,也没说不能做产品,只是说这个东西不是最优的,在完成相同的指标下,该电路结构复杂,功耗大,面积也大。你用这个构架做了很多东西,不代表这个是最优的。

TI还有很多LDO的paper呢,你真以为他们发的paper里的电路综合性能就好啊,大部分都不实用,包括这个。而且他们发这个paper,不代表他们产品就这么做。你说你用这个构架做了很多东西了,难道你现在都没发现它的很多问题么?(面积,功耗,性能)

我没说它的综合性能好,analog就是一个trad off, 没有一个东西在任何情况下都是最优的!曾经有客户提出高增益、无线带宽要求的。

这个架构本身真的很简单,一点不复杂,也可以再简化一点,前面也有人说了,有多家产品在用(我就知道台湾一家也再用),不仅仅是我用过(我用过的架构多了,包括自己创新的)。它有缺点(最大的就是,PowerMOS gate不能拉到0V,需要较大的area),但也有优点,例如瞬态响应、PSRR。

做产品,不等同于做学术和研究。不仅仅是performance和成本的trad off,还有开发时间,测试方便性....这些综合因素。 在给定的开发时间内,选择合适的架构,满足给定SPEC要求,达到高的产品良率(paper上常常不会考虑这点)和可靠性,满足客户应用要求,以市场和客户为导向。 其实做产品就是上述所有这些因素的trad off,不仅仅是performance.

这贴,我的回复到此为止吧,论坛里面讨论技术问题,常常都会跑题,扯到十万千里外争论其他的东西。

你说的它的优点,别的更简单的构架可以轻易实现,而且面积,功耗都小很多。就是因为这个我才说它是瓷娃娃,中看不中用。

这个ldo就给数字用的吧,psrr和噪音不看好..瞬态在100ma@1us下,跌落pvt超过10%不? 可以带多大的负载电容,对最小负载电流有要求没?