LDO负载能力差是什么原因?

时间:10-02

整理:3721RD

点击:

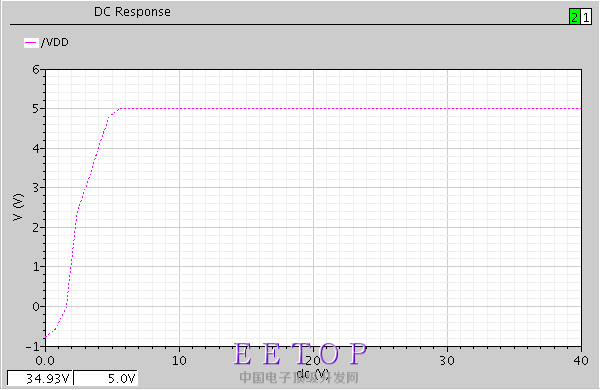

LDO稳压输出为5v,在进行DC仿真时,负载接的是一个理想的电流源,扫描从0~5mA,发现电压在1u左右降到0v以下,并保持不变。请问这是什么原因?路过的大神请不吝赐教啊!

你LDO的功能可能就有问题,先查查看。

power管能力够吗

环路dc点对吗

发现电压在1u左右降到0v以下?这句话是什么意思?没明白。不过你这个应该是LDO输出级有问题。

1u是什么意思?

大电流正常小电流无输出?可以观察下power管栅压的变化

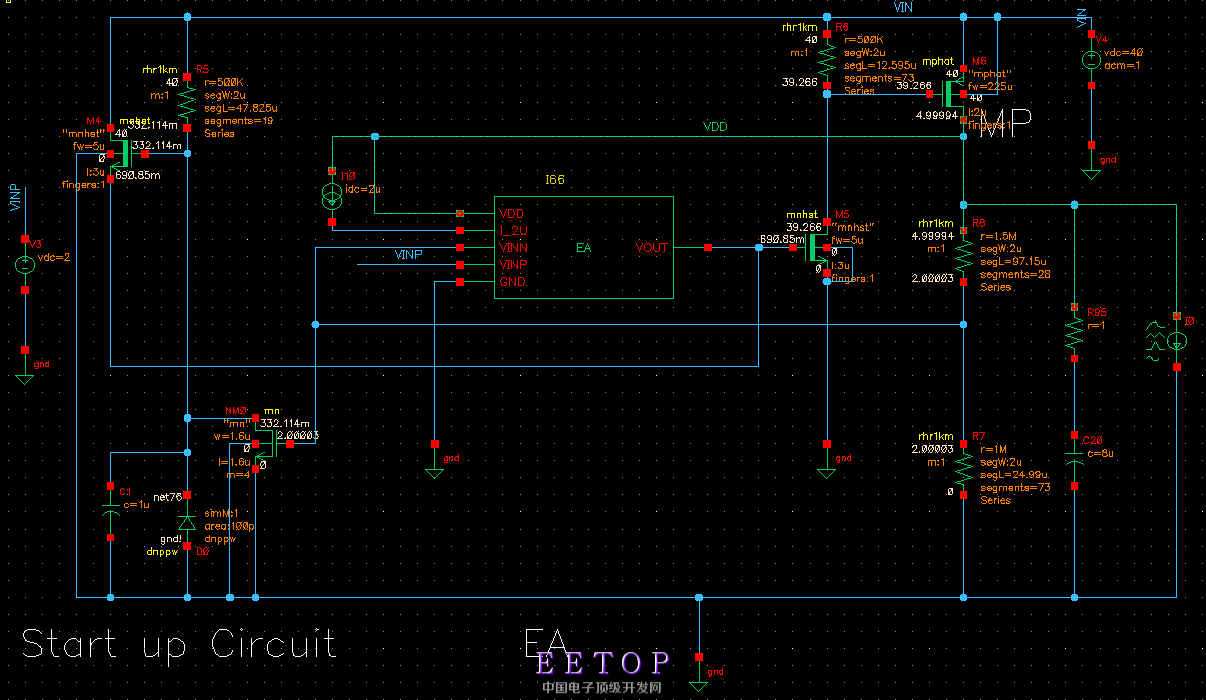

嗯,是power管栅源电压的问题,因为我的是高压工艺,而误差放大器是5V供电,输出太低不能很好的调控power管,后来加了一个升压电路,可以实现了。

嗯,谢谢,已经解决了。

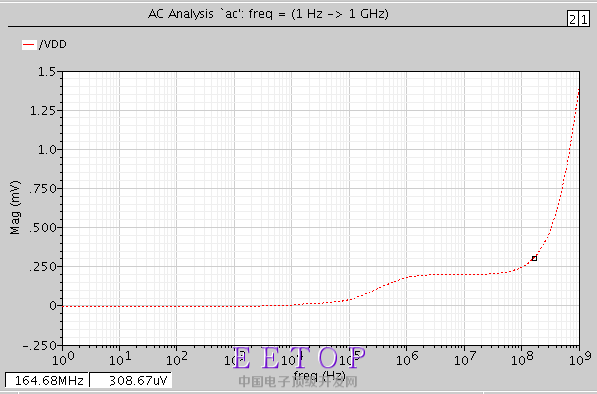

是power管栅源电压太大的问题,加了一个升压电路解决了。 现在LDO的静态电流,负载电流,线性调整率,负载调整率,电源抑制比等性能都达到要求了,可是环路交流仿真出问题了,环路增益基本为零,这又是什么原因啊?

你怎么仿的交流增益,截个图看看

调整管 MP为40v高压管,仿真时直流电压为40V,交流幅值为1v。直流仿真输出为稳定的5v,交流曲线显示LDO环路无增益,这是什么原因啊?

交流訊號輸出是VDD, 輸入在哪?

40V電壓源嗎?你的ac仿真是VIN上加了个acm=1,然后看的VOUT吗?

这样仿真的是PSRR,而不是环路增益你这测的不是环路增益,是PSRR了。

嗯,原来仿真错了,现在解决了