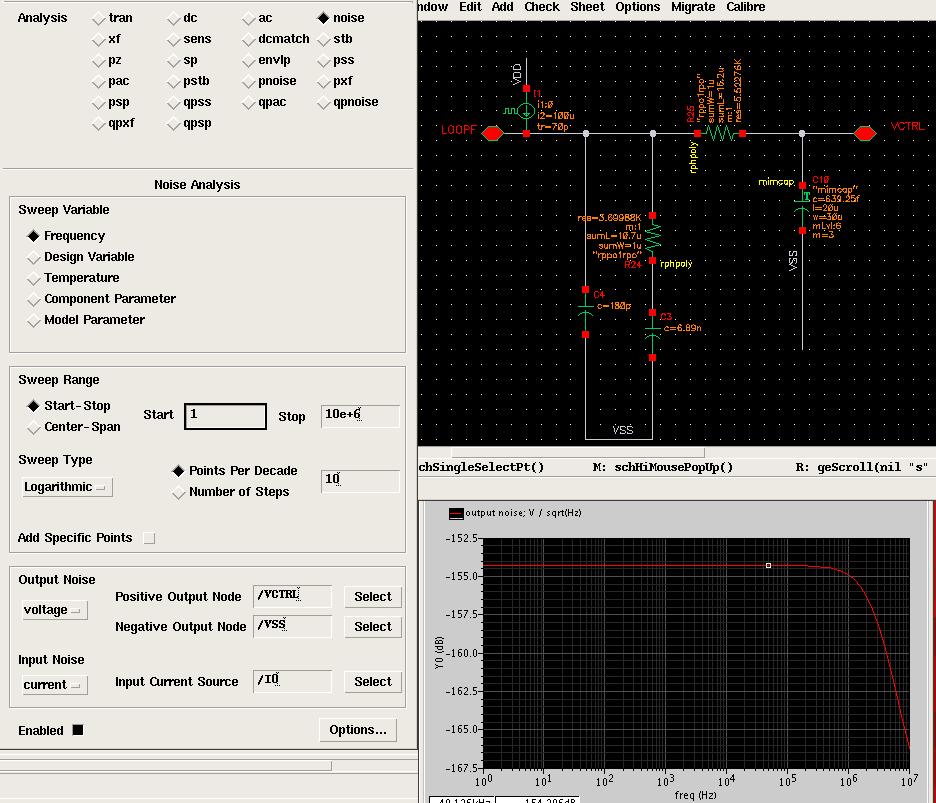

帮我看下PLL中LPF的noise 仿真对吗?

下面是我的设置,和波形,对吗?

要加电压偏置吗? 我知道该怎么加才好呢。

请指教!

kool, 快现身啊,帮帮忙啊。谢谢啦!

不用加输入,计算电路内部噪声时不会用到输入电源,只是算NF,输入等效噪声时才会用到输入电源;

另外LPF的噪声是与Vctrl无关的,可以认为是一个线性电路,所以也可以用noise仿真,也可以直接计算。

你可以比较一下下面几个方法的结果:

1.像你那样设置仿真。

2.PSS+PNOISE不加输入电源的输出噪声。

3.用noise仿真。

4.直接用公式计算输出噪声(可以用用matlab或其他工具画出来)。

这四种结果应该是一样的。

好的,我一个一个试一下。

谢谢!

我都仿过了,是一样的结果。呵呵。我可能还要继续消化一下你讲的。

做了noise 仿真,我 printnoise summary , 看2个电阻的热噪声。发现:

R24(提供零点的电阻)的热噪声贡献随着和它串联的电容C3值变化而变化, C3很大时,等于4kTR24了, C3变小,噪声贡献就小于这个值了。这是为什么呢?

R25( 提供第3个极点的电阻)噪声随其他device值变化很小,几乎就是4kTR25...这怎么理解呢?

对了,以上我说的都是频率比较低的时候。

怎么这么多广告?

我们就做芯片的,谁会需要买这些东西啊。

这个你可以推算一下两个电阻贡献到VCTRL的噪声,这个很好推导的,但是要有点耐心。

直观上来给你解释一下,由于C10很小,低频时,它的阻抗远大于其他部分,所以R25的噪声几乎都传到了输出端(电阻分压原理)。

对于R24,首先用戴维南将R24,C3,C4以及串联在R24上的噪声电压等效成一个电压V1和阻抗Z1串联,那么当C3远大于C4时,V1就等于R24的噪声电压(C3变小时,V1变小,这就可以解释你说的现象了),然后再将Z1,V1放入LPF中,很显然,低频时Z1远小于C10的阻抗值,所以输入噪声也是接近4kTR24。

推导了一下,明白了。谢谢你,每次都讲解得很清楚。只怪我离开校园后逐渐变成了spice engineer 了。oops... 要改变一下了。

另外,通过仿真CP的噪声,得到的噪声单位是A/sqrt(Hz)..。乘上传递函数N/Kcp *(Hol/(1+Hol)), 的到的单位是 1/sqrt(Hz)。 而VCO 的相噪是dBc/Hz...怎么样把它们一起叠加到PLL的相噪呢?

同理,LPF 的噪声通过传递也是1/sqrt(Hz) 的单位。

kool:

我想做一下LPF的ac 分析, 看零点极点情况。输入我放电流源,ac 1, dc 243u,放这个dc 是想让VCTRL片置在0.9V) .. 可是,看dc输出,vctrl 怎么都不是0.9V, 要么是负的无穷,

要么是正的无穷。

然后我在各个地方尝试加dc电压源0.9V,

这样也不行,仿不出了,因为强制它了,结果都是0 了。该怎么办呢?

有何妙招?

VCO得到的相位噪声L(f),所以需要转换成相位的噪声功率谱S(f)。两者的关系是: L(f)=10*log(S(f)/2)。将放置得到的L(f)专为S(f)就可以用传输函数计算了。

你的电容仿真的时候是MOS电容吗?不是的话与Vctrl无关的。

谢谢啦!

有点疑问:这个公式看上去:S(f)/2 表示 只考虑单边,是吗? 然后,把它转换成 DB 了。实质上,L(f) 和S(f)一回事儿?

我用的理想电容。

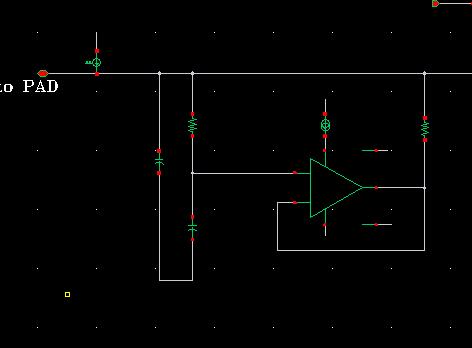

可是,因为我想尝试下有效电容增加,所以,有一个运放,这样就要dc电压合适才行。如下图。 我没法仿了。

另外,我也开始仿div2 了。

2分频电路的相噪仿真是把它和VCO一起访呢? 还是单独访?

我之前是一起仿的,因为这样可以看出div2对VCO相噪的影响。但是一起仿的话,这个结果要转换成对整个PLL的相噪的贡献的时候要用VCO 的噪声传递函数(高通),还是用divider的相噪传递函数(低通)呢, 就搞不懂了。请指教!

对不起哈,太多问题垃。

不是一回事,一个是两个噪声的比值,一个是相位的噪声功率谱密度,你可以看一下清华池保勇写的CMOS射频集成电路分析与设计那本书,或者其中的频综方面的书。

这个确实不好加dc电压,我试了一下,你可以用一个直流源串联一个很大的电阻,我串了1P(=1000T)欧姆。这样这个电阻几乎对LPF不会产生影响了。

能不能一起仿就看你的PLL是从VCO输出还是从div2电路后面输出,如果在VCO后面输出则不能一起仿,在div2后面输出的话可以一起仿,但是一般divider的噪声对PLL影响很小。

能说说你这个电路中有效电容增加的原理吗?呵呵。

哈哈,搞清楚了。

我看了,大概明白了。

这本书还第一次听说,真是落伍了。

还是第一次听说这本书。刚才和同事借了,大概明白啦。我本来就是很疑惑,等式的左边是一个相对量,右边是一个绝对量,不太理解。

PLL输出是从div2 出来的,给其他模块。

可是芯片回来测量的话,只能测vco的输出,div2没有可测量的输出。我的div2 对vco 好像有将近1dbc/hz的恶化,是不是太大了?

我的电容太大,想把它做进去不容易,所以想试下电容乘积一类的方法。可是,心里不踏实,我还从来没有在LPF那里加过这些东西。怕他们带来的噪声。带宽,偏置。

您一看就明白啦!

Keliu Shu的书上134页也有讲。

good idea. 可以行得通。谢谢啦!

你有做过capacitance multiplier 吗? 我想尝试,就是没底,所以很担心。流一次片也不便宜呢。

那你们为什么测VCO的输出而不直接测PLL的输出呢?不过也没关系两个地方的相噪声测出来的结果应该是一致的,但是从div2输出测的相噪声理论上比vco那点测出来的相噪声好6dB.

你说div2对VCO的相噪声有1dbc/hz的恶化是怎么比较的?每个频偏处都是这样?

在学校时抄过一个含三阶LPF的PLL,流片能工作,就是当时很多都不懂,看此帖深入了不少,呵呵

我也没做过有源的LPF。不过我看你的电容很大,环路带宽应该很窄,30KHz左右?你的Icp, Kvco是多大?你可以减小这两个值来减小你的电容值。不过要考虑到噪声,其中减小Kvco对噪声的优化是有利的,但是减小Icp会增大PFD/CP贡献的噪声,这个要注意,

做有源LPF的话,应该要注意运放的噪声和速度。你的PLL带宽较小,而对LPF来说,它到PLL的输出是带通的,所以在运放在10-100KHz的噪声对PLL的噪声影响会比较大,而且在这个频率处,flicker noise会比较大的,所以管子的尺寸不能太小,速度方面的话,我觉得运放的UGB是不是得至少大于fref,使LPF的电压在下一次的PFD/CP比较前能够稳定?对运放做稳定性分析的时候,应该如何考虑运放的负载呢?

感觉做有源的LPF还是比较有挑战性的。

我们的测试芯片 有外挂VCO的2个pin, 这里可以测。div2的输出比较敏感,我想不出什么好办法测它呢。

单独测VCO, 得到 相噪。把它和div2串联,再测vco的相噪,发现恶化了。所有频点都是这样呢。

环路带宽是比较窄,40 k. 如果,减小icp 到60uA不知道还行不,我式以下吧。Kvco 变化范围很大,因为频率范围很宽,除非用几个vco,这样又面积太大。

active LPF 我也不是很敢做呢。 OP的带宽能做到 几十Mhz, 速度应该可以。但它的loading 我也晕着呢。还有,它的引入,改变了LPF的传递函数呢?这个我也弄不清楚了。

不对吧,你串联div2后看的哪个输出的相噪声?VCO还是div2的输出?

从VCO看的话应该会差一点点,但差别可以忽略,但是pnoise中relative harmonic要改为2。

从div2输出看的话应该是要好将近6dB的。

频率范围多宽呢?用了几位的SCA?Kvco有多大?