为什么放大器闭环后会出一些问题

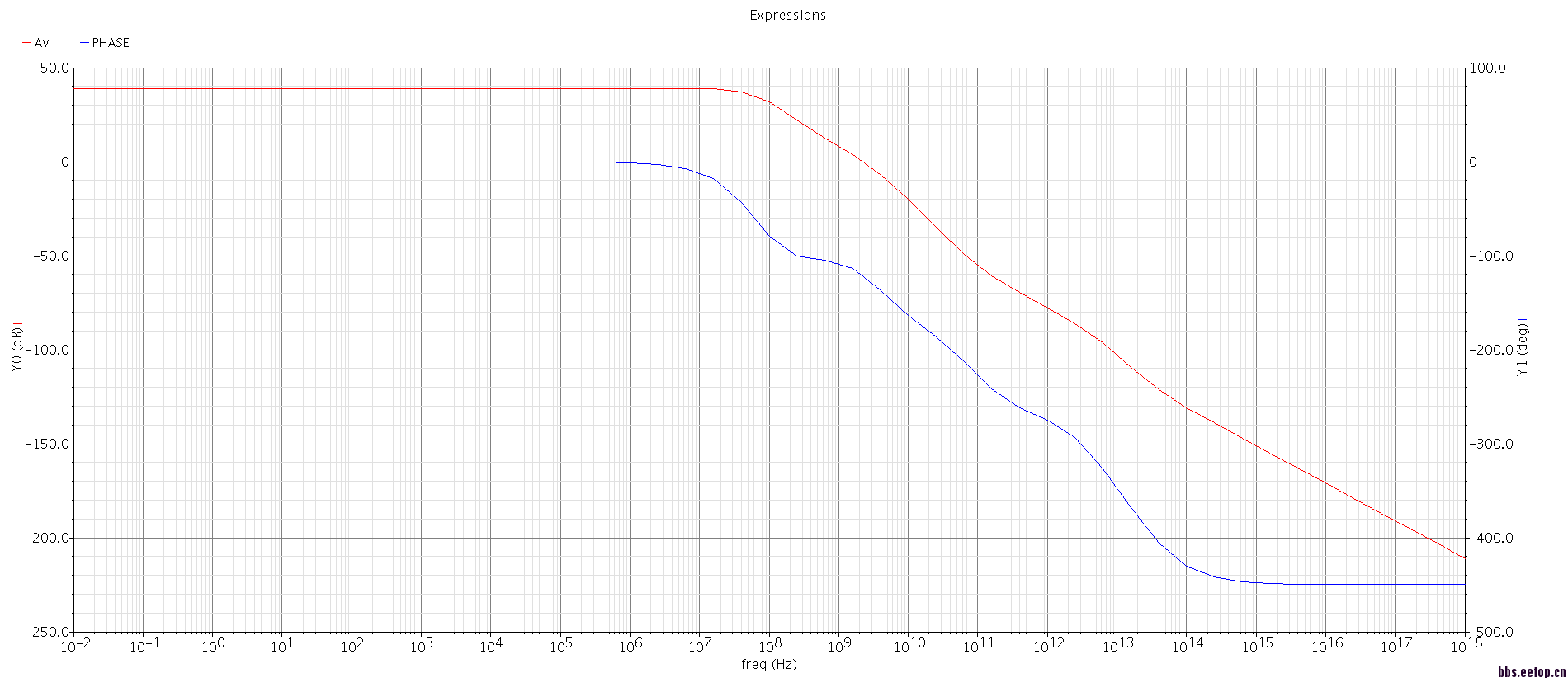

开环曲线我已经调好了,GBW=2G,Av=38dB,空载

一接闭环后

GBW变成400多M不说,感觉都不稳定了,这是为什么啊,求助

运放是用在1g速度反转的电荷泵里的,电荷泵对运放的指标有什么要求么,顺便问一下,谢谢

如果不接负载的话,单纯的放开环的相位裕度是没意义的。

不是自身有负载cds么?

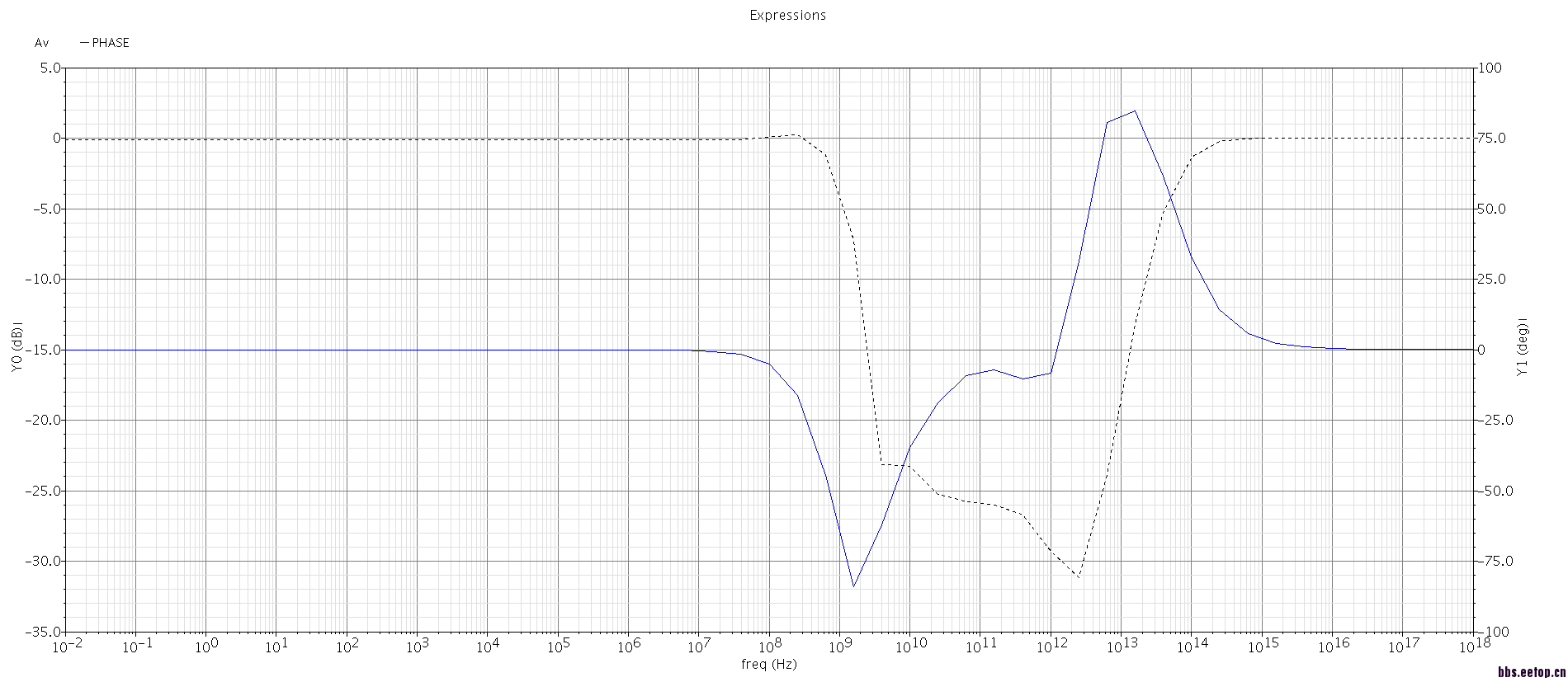

LZ大概知道怎么回事了,明天去实验室做一次STB分析,还有请问一下,为什么频率升到1e14时,闭环增益又上去了呢,谢谢

被吞贴了--,LZ大概知道怎么回事了,明天去实验室做一次STB分析,还有,请问为什么增益在极高频段又上去了呢,请问,这个怎么也想不明白啊,thx~

你是说在高频时,闭环增益有一个凸起的意思吗,就是增益升上去,又下降?

是的啊,不解,能指点下么

感觉还没有入门啊。对于简单cascode结构的零点不清楚,也不懂loading的作用。

先说loading吧,空载是不可能的,就像你现在这个case,闭环时候gate接到输出,就是一个loading,估计有几十fF,实际上还有各种parasitic。

再回头看这个结构的pole,或者说要把bandwidth做高,limitation 在什么地方, 镜像极点和folded点是两个频率有可能的bottle neck。单级opamp输出极点是主极点,需要提高带宽,同时保持一定的phase margin,那第二第三极点一点要高。或者说带宽做到第二个极点1/3处,也就能保证60deg左右的phase margin。

那再看看schematic上的device size,都是一些很不合理而且没有依据的尺寸。

还有一点,仿真frequency 10^-2 ~10^18有意义么,不要钻牛角尖

说的很狠,但全是大实话,LZ模拟门还没摸着边……

额。我知道了。LZ确实是新手,还有很多东西需要学习,以后会努力的。最后的解决方法是加了1pF的负载,把主极点强行拉了下去,因为我这个运放没有速度的要求。

还有请问一下为什么我管子的尺寸设计不合理呢,我是这样想的,提供电流的管子可以把L做大一点,提高ro2。cascode管可以做小一点,减轻自身负载。还有“镜像极点和folded点是两个频率有可能的bottle neck”这句话是什么意思啊

希望能得到您的回答,谢谢了

九楼说的有道理,你遇见的情况从传输函数看,是在某一频率下,分子变小引起的。建议小编听从九楼的建议,从基础学起,单纯的仿真是没有意义的。

就这个电路,你想通零极点了,也就通了,

恩恩零极点要弄清楚