请教---小问题

时间:10-02

整理:3721RD

点击:

此前,小弟曾经在论坛上发过一篇“劳动成果共享之二———电流镜设计报告”,当时年少无知,初涉模拟,许多问题考虑歉妥,诚向同学们道歉。

之后,有位同学给发了建议,个人觉得非常重要,他来信提到:

1。cascode device L取最小尺寸即可;

2。Vdsat的分配比例3:2或3.5:1.5更好。

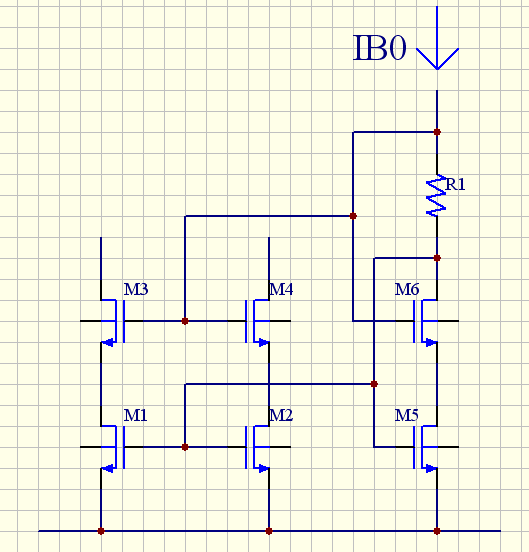

现在,小弟又要搞个OTA,碰到同样的问题,觉得很有必要“如这位兄长所述的一样”优化一下,但对其中的道理不是很明白,具体电路是常用的

自偏置共源共栅电流镜,如图所示。

附带一个疑问:咋样直接贴个电路图,讨论电路问题,直接贴个图特别适用啊!

之后,有位同学给发了建议,个人觉得非常重要,他来信提到:

1。cascode device L取最小尺寸即可;

2。Vdsat的分配比例3:2或3.5:1.5更好。

现在,小弟又要搞个OTA,碰到同样的问题,觉得很有必要“如这位兄长所述的一样”优化一下,但对其中的道理不是很明白,具体电路是常用的

自偏置共源共栅电流镜,如图所示。

附带一个疑问:咋样直接贴个电路图,讨论电路问题,直接贴个图特别适用啊!

没看懂你的问题

怎么能用电阻呢?

个人认为:靠近地的一层对匹配精度影响大,因此L应该取大,因为Vt、beta的不匹配直接反映到Vgs;上面一层L取最小尺寸可以抑制耦合噪声

个人认为:靠近地的一层对匹配精度影响大,因此L应该取大,因为Vt、beta的不匹配直接反映到Vgs;上面一层L取最小尺寸可以抑制耦合噪声

怎么能用电阻啊?

这种电路应该经常用在双极电路里。CMOS中晶体管的成本很低,比例精度又高,应该用晶体管搞个偏置才对。电阻即不准又浪费面积,非常不明智。

電阻的確很浪費面積

用MOS取代會比較好

小弟我真是見識到拉~

基本同意wins2000sp3兄弟的观点,MOS版本的cascode电流源电路在David Johns和Ken Martin的书里面已经讲的很清楚了。

这里面R1的作用就是来调整M3 M4的偏置电压的,我看直接调整M6就可以了,不然再添加一个MOS管多麻烦啊。M6是不需要和M3 M4匹配的,楼上兄弟同意否?

不喜欢这种电阻自偏置的bias,管子尺寸大了还可能碰到不稳定的问题。

CMOS工艺里,很少这么用的,我是从来没见过别人的设计里这么搞。

acdamic一点,要求高一点,就参照paul gary的书。

懒惰一点,要求低一点,用一个长管子就拉倒了。

要求不是很高的低频电路里这种结构非常常见,包括TI.NS,LINEAR的电路里都有这样的结构,

同意楼上~!