关于差分运放的仿真

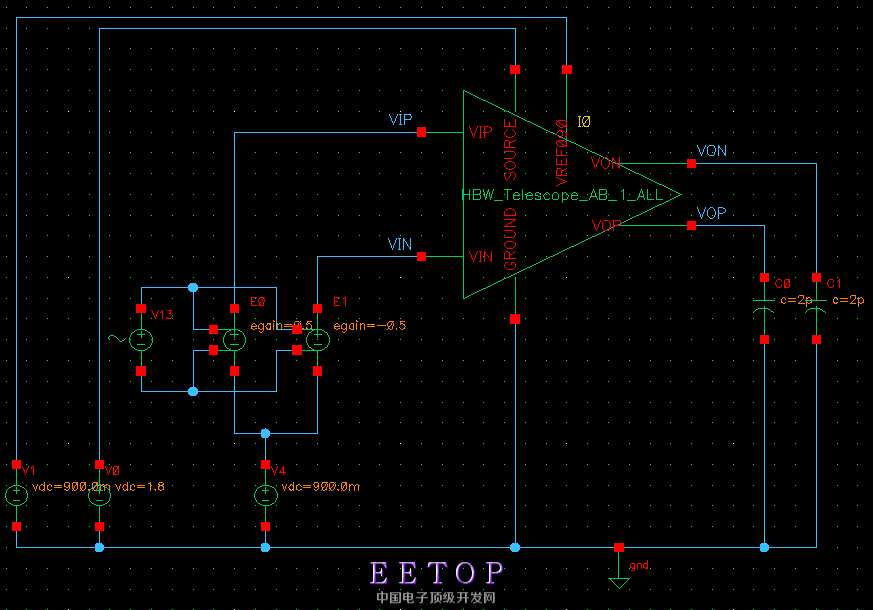

电路图如下

仿真的时候有两种表达式

AVV=dB20((VF("/VOP")-VF("/VON"))-(VF("/VIP")-VF("/VIN")))

PVV=phase((VF("/VOP")-VF("/VON"))-(VF("/VIP")-VF("/VIN")))

A=dB20(VF("/VOP")-VF("/VON"))

P=phase(VF("/VOP")-VF("/VON"))

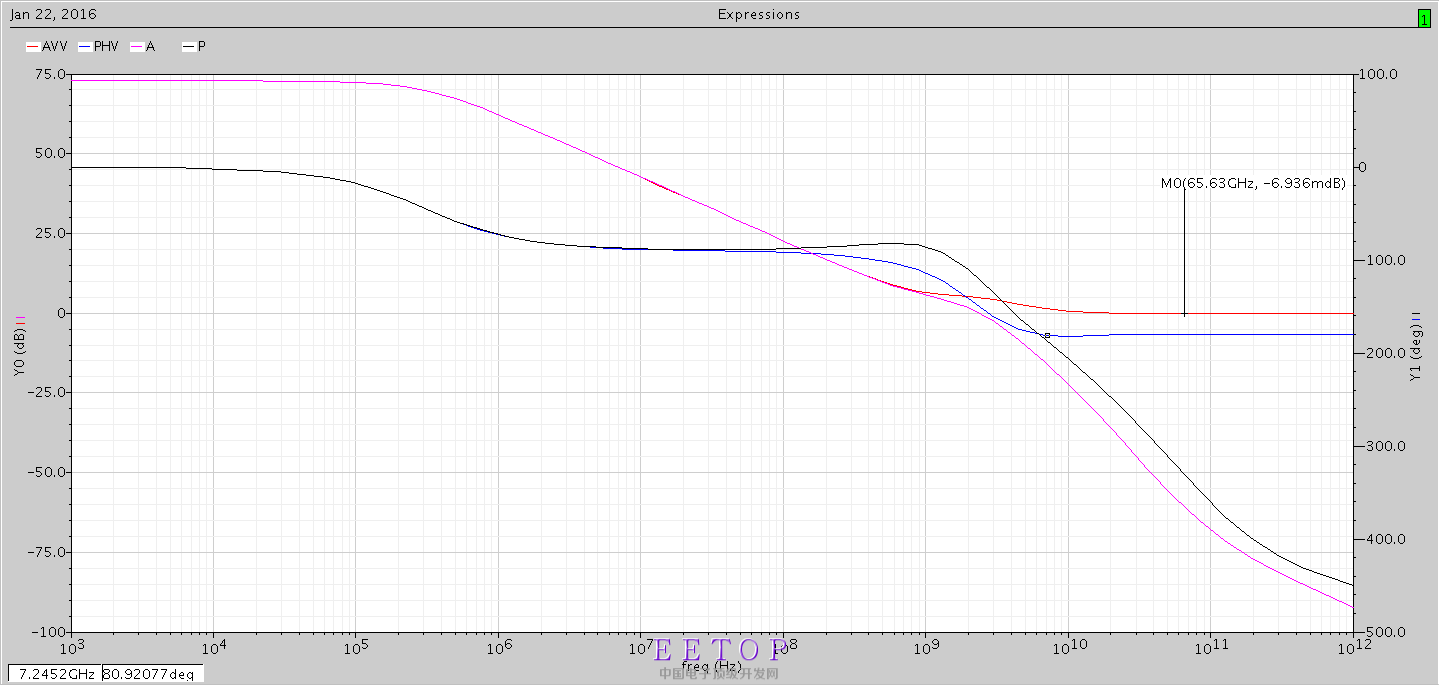

仿真结果如下 凌乱了 不知道信哪个 两种表达式的结果不应该是一样吗 AVV和PVV看起来很奇怪啊AVV下降到0dB以后不再下降同时PVV达到-180也不再下降

我感觉应该是A和P是对的 某教材上也是采用的A和P的表达式 但是看起来AVV和PVV才是最完整的表达式啊

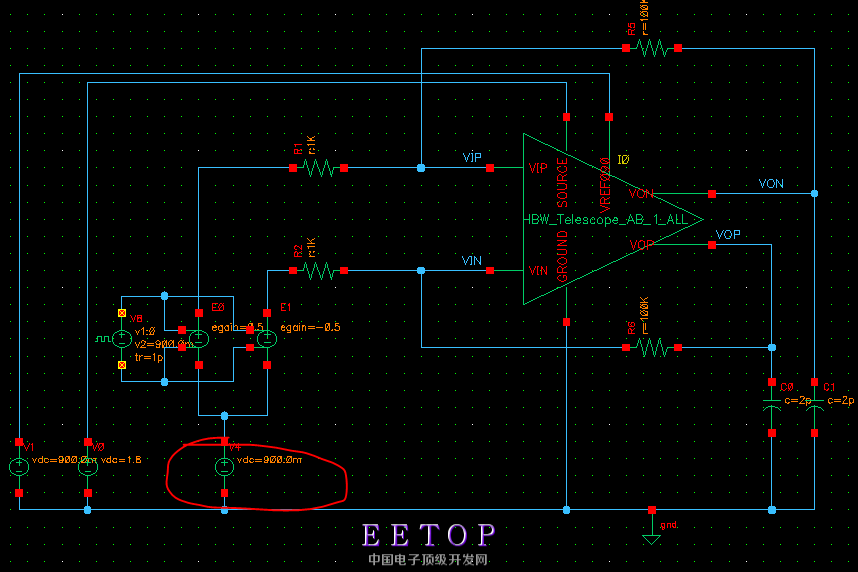

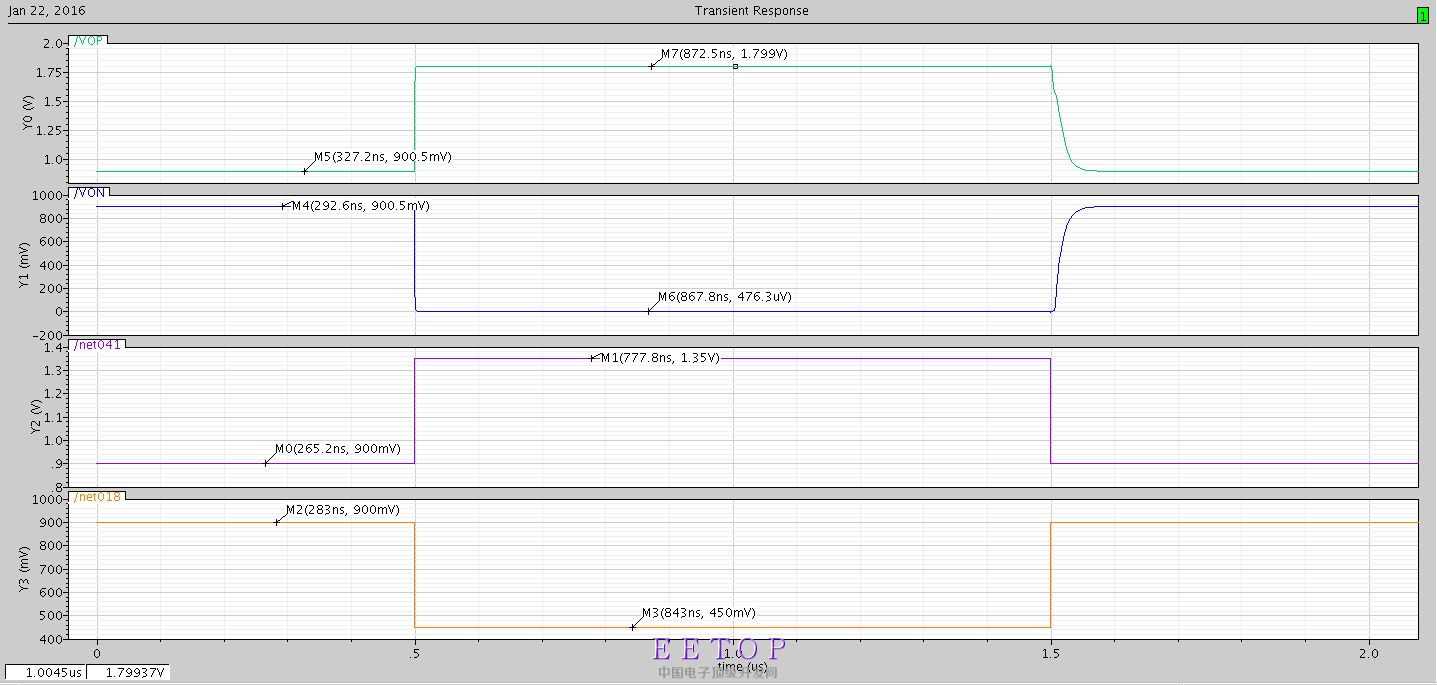

2.怎样仿真SR和settling time

运放共模输入和输出都大约是0.9V,那么V4(图中红色圈)怎么取?是不是要先扫描V4找到使得运放正常工作的V4,然后再仿真?

图中4个电阻怎么取?电阻取值会影响使得运放正常工作的V4。

(1)我是这样设计的,输入共模电压0.9V时输出共模电压0.90045V,希望V4=0.9V时正常工作,仿真显示需要电阻之比图中R1:R5=1k:100k。接下来是不是把输入的阶跃信号加上就可以仿真SR和settling time了?

(2)有些教程上是直接拿开环仿真的SR,直接输入共模电压加阶跃信号0-1.8V,看输出端的波形算SR和settling time 个人感觉不靠谱,不知这种方法对不对?

小弟对模拟还是挺感兴趣的,以后读研也是模拟、射频的方向,最近做高带宽运放看了不少高水平的文献,之前做提高带宽、增益、共模反馈和频率补偿还算顺利,就是做瞬态仿真不清楚全差分运放瞬态仿真的方法,也查了论坛里的一些资料,方法也是五花八门,但都没有具体说明怎么做。不知道有没有写的比较具体的全差分运放仿真规范?感觉这方面的资料好少,仅有的几份资料也比较含混不清(可能是我水平太低)。

希望各位前辈帮帮忙,祝各位身体健康、工作顺利。

philosics, 你好。

这些问题,在坛子里都有过比较深刻讨论,可以搜索一下。

比如,第一个问题,可以参考这个帖子http://bbs.eetop.cn/thread-301540-1-1.html

您好,谢谢您的解答。那个帖子是仿真的闭环稳定性,我这里第一个问题是想看看开环,并不知道如何解释奇怪的AVV和PVV曲线。不过看你发的链接还是学到一些东西,非常感谢。

第二个问题我再论坛里找了好久也没找到满意的答案,看到一些帖子说用两个balun仿真,帖子中的资料也没有提及如何仿真SR和settling time。另外balun怎么用我也不会···(怪我太菜)。

祝您一切顺利。

增益应该是输出除以输入,再取等dB20。或者反过来

学习了。

我也遇到这个问题了,这里不需要共模负反馈吗

第一个问题我不知道你使用什么画的,一般是直接由各direct plotac phase就可以画相位了呀。我用的是adl xl, 不知道你用的什么画的。

第二个问题,sr的测量一般采用闭环,因为OTA会有offset,而ota稳定性一般还好,所以用自偏置,之后可以不用再去管offset,如果用开环的话必须去补偿这个offset才能去侧gain,sr之类的。

至于输入电压,首先你得去看crm的输入范围。具体办法就是加上CMR电压后,看个个管子是不是工作在正常状态。这样测出的范围就是CMR的范围,之后你选一个电压侧SR就可以了。一般设计都是先保证CMR范围,让管子都工作在正常区域。再去考虑gain,sr之类的东西。

希望对你有帮助

看来你还是没有理解,其实这连个表达式都可以,第一种在任何情况下都可以用,第二个使用要注意,将ac mag 的值设为0.5,这样的话归一化后输入差分相减为1 就是第二个表达式

你好,我也是刚接触模拟,想请问一下全差分的仿真要怎么仿,失调电压,共模输入范围还有其他的