求助大佬PLL在AMS下的stb仿真

时间:10-02

整理:3721RD

点击:

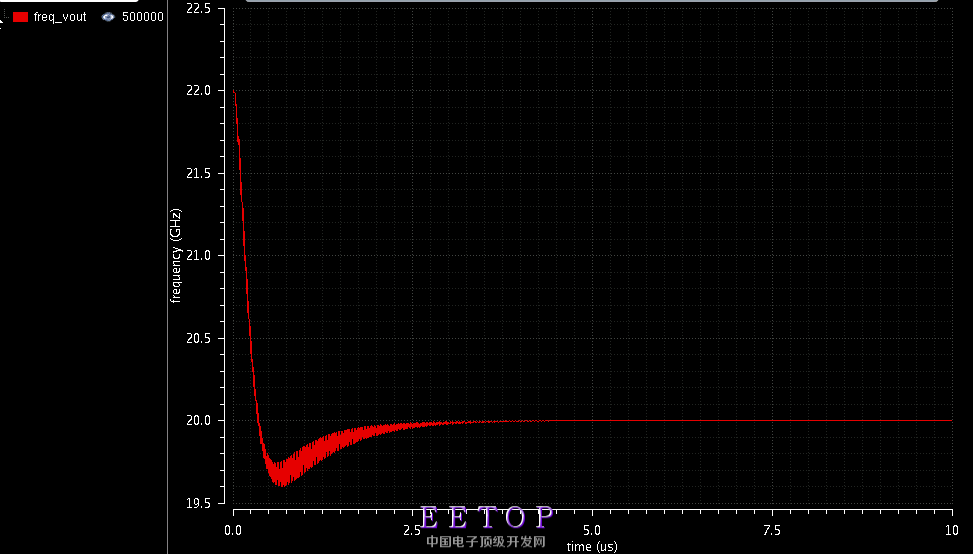

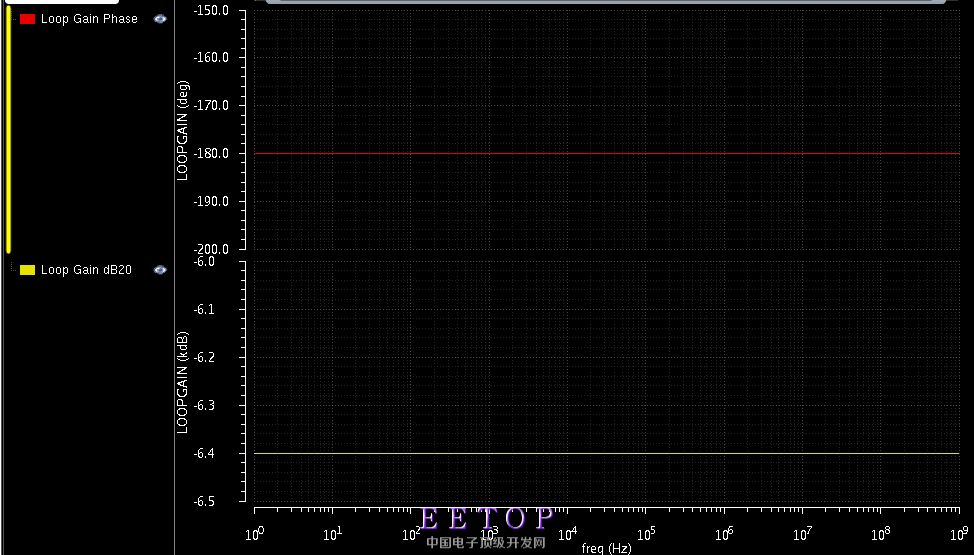

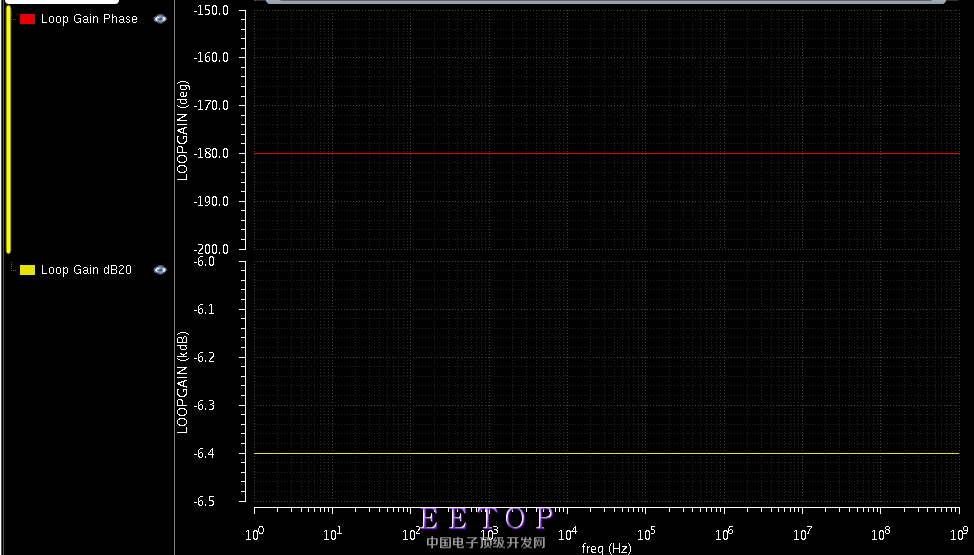

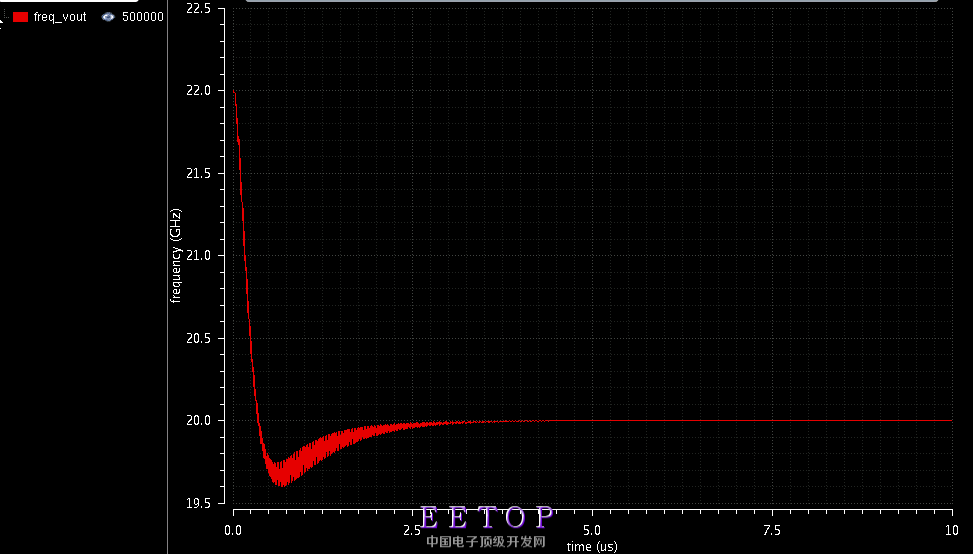

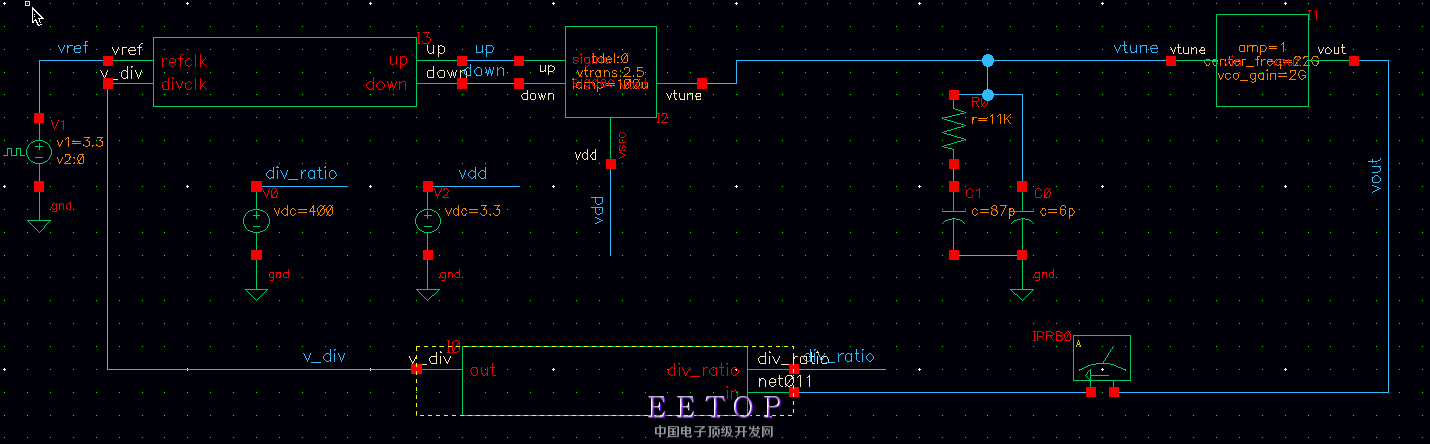

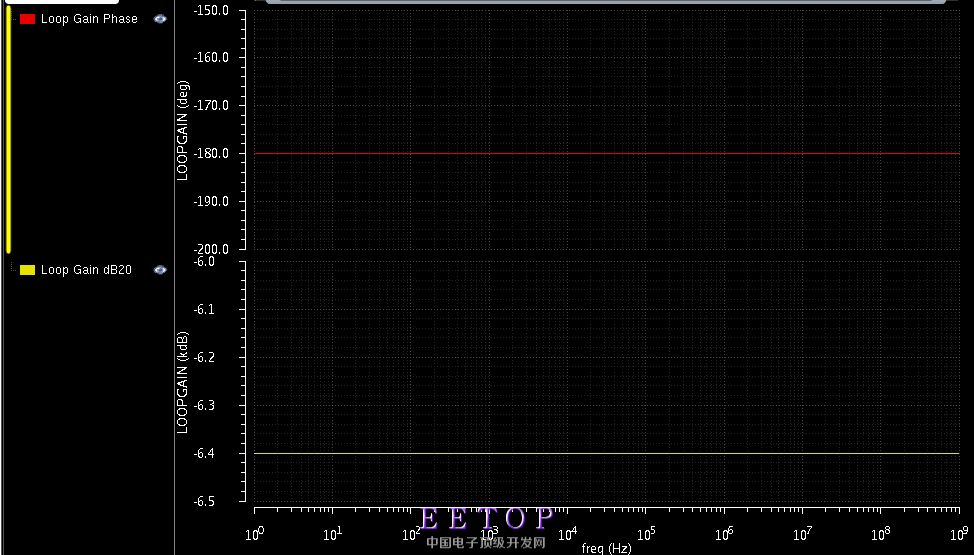

如题,我现在用Cadence搭了PLL的各个小模块的VerilogA的模型,在仿真相位裕度的时候出现的结果实在太奇怪了,我想求助下PLL在Cadence下的stb仿真是怎么仿真的?仿真tran是没问题的。运放仿真stb是有个静态工作点的,但是现在这个PLL是没有静态工作点的,是一直跟随瞬态变化的,这个的stb是怎么仿真的呢?还是说我一开始就搞错了,我建立的是时域的行为模型,是要相位域的行为模型才能仿真stb吗?如果是这样子的话那么相位域的模型是怎么建立的呢?下面的图是原理图跟仿真结果

这个是原理图

这个是stb的仿真结果

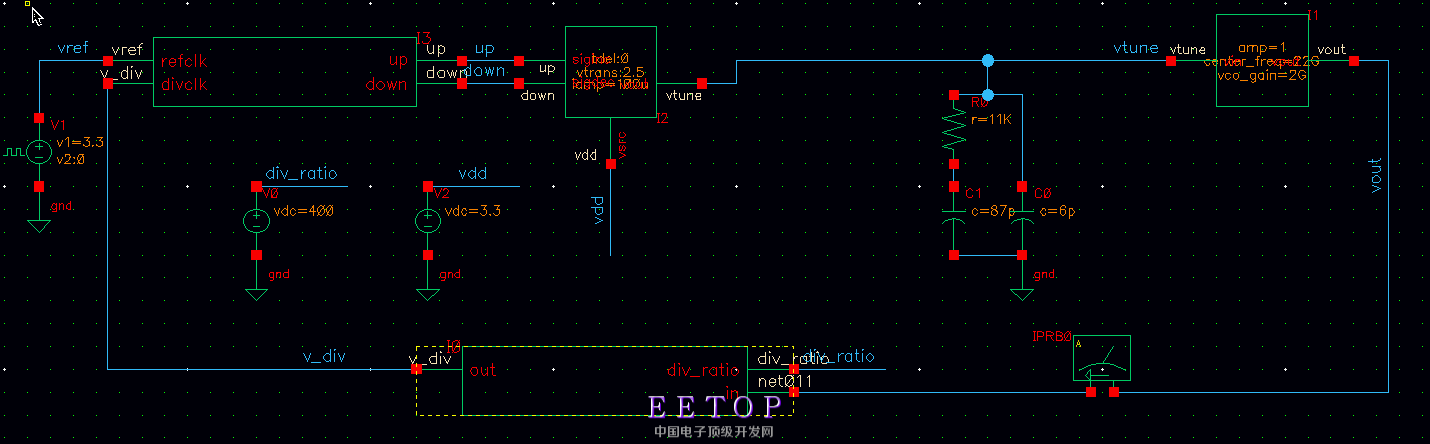

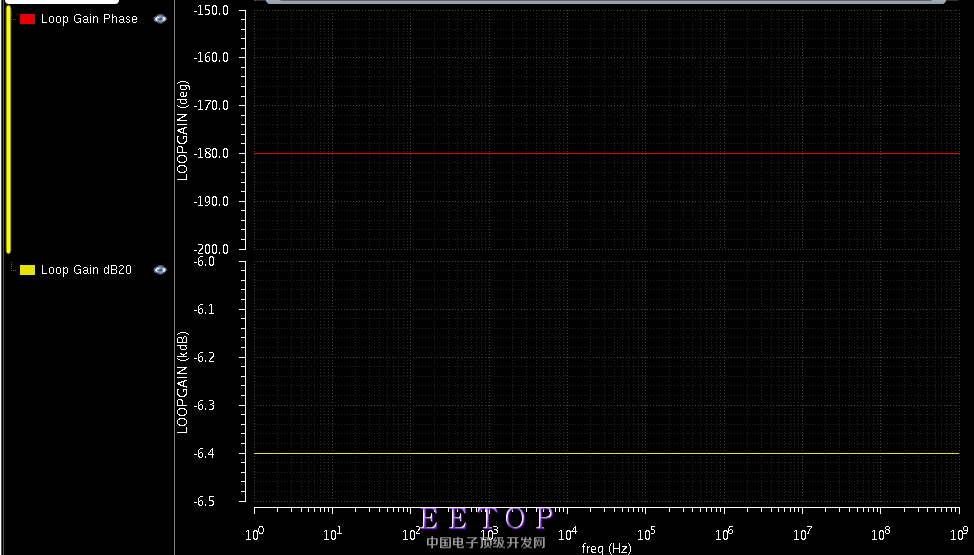

刚才发现图不见了,重新上传下原理图跟stb仿真结果

不知道图片为什么没显示出来,重新发下图片

这个是原理图

这个是stb的仿真结果

你有把一些 non linear 做成 linear model跑嗎?

这个好像没有,我现在做的是把每个模块都用VerilogA建行为模型。是要所有模块都用线性模型才能仿真stb是吗?线性模型是不是书上说的那种相位域上的传输函数啊?

PLL实际上是一个离散系统,在锁定后可以等效为线性系统,所以你应该把各个模块抽象为相位域的模型,STB仿真的前提是线性系统。相位域的建模很简单的,matlab和Verilog-a都可以很好的完成。当然离散系统用PSTB也可以完成相关的仿真,前提是你整个系统工作频率相差不大,不然收敛性是个很大的问题。

恩恩,谢谢