用一个TSPC型D触发器构成二分频器,触发器调到什么程度才可以

时间:10-02

整理:3721RD

点击:

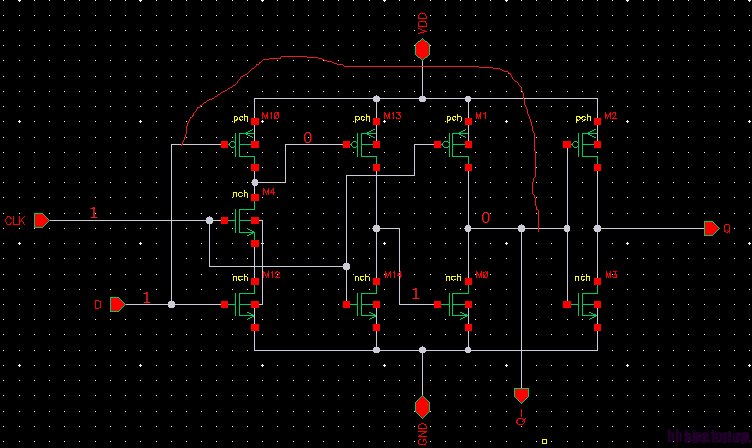

我最近在调一个二分频器,用的TSPC结构的D触发器。单独仿真D触发器发现出发出来的信号非常小,不符合D触发器的原理,但是接成二分频器的结构是可以分频的,我是在5GHZ下分频,用的是65n的工艺。为什么D触发器无法正常出结果,但是分频器却可以正常分频呢。

仿真方法?

详细的电路呢?

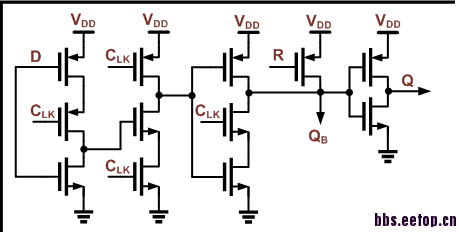

这是 E-TSPC ,工作频率不能低,G级别 。你是不是时钟太慢了

我的时钟是5GHZ,应该还好吧,或者高一点到8HZ也可以

Check input swing: u need rail to rail input

Check the raise time fall time and leakage current when TSPC branch clock off.

你是不是在做分接器

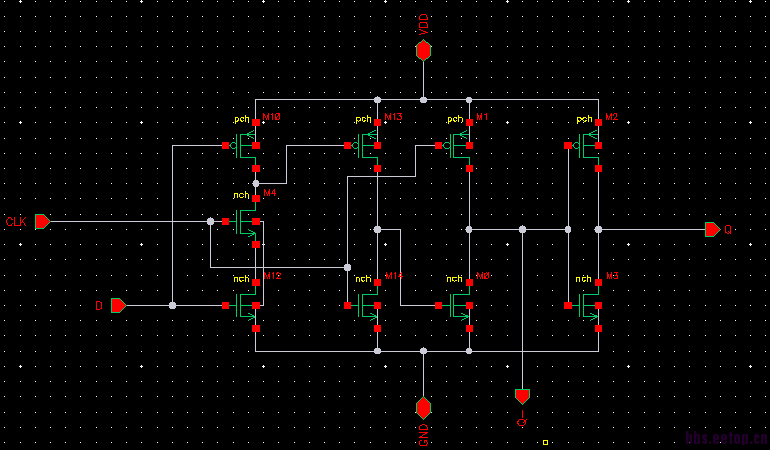

第三级中间缺个管,逻辑传不过去

是啊,就是在弄这个做分频器

是轨到轨输入,上升时间和下降时间不好说,因为都下(上)不到所要求的电压,就不谈上升下降速度了

我试过你这个结构,结果是一样的,我这个结构是改进的TSPC,分析了一下时序逻辑也是可以的,

依照你的图,下面两个问题你是怎么分析处理的

1. CLK为正时, M14和M13抢逻辑

2. CLK为负时, M1和M0抢逻辑

3. DFF的前后两极 锁存-触发 体现在哪里

4. 补充一张图,假设M13比M14强,CLK为1时,D为1时, Q-为0,此时Q-接到D.....

谢谢分享!一起学习。

看看你的 D 与 CLK信号的时序,是不是你在仿真的时候,弄成 D 与 CLK 同时翻转呀?

mark。