大家做bandgap精度能到多少啊?这样的BGR有优势吗?

大家做bandgap电压基准的精度到多少啊?

一般好像温度系数都弄得不错,到几十或者十几个ppm/c

但是好像很少考虑电压基准的初始精度哦

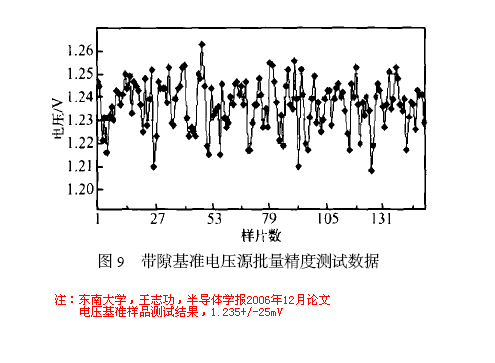

比如:设计1.23V的基准但是流片出来会变成1.23V +/-20mV或者更多

那么那十几个ppm/c的温度稳定性是否还有意义呢?

大家做bandgap跑工艺角的时候是不是也发现类似的问题,得到三个工艺角下

的三条温度特性曲线离得很远呢?

比如在室温下,FF角:1.25V,TT角:1.23V,SS角:1.21V

这里我要指出的是:这里的工艺角是BJT的工艺角,MOS管的工艺角对bandgap的影响不大,记得有一次,我师姐用CSMC上华0.5的工艺库作bandgap,跑工艺角,还非常好,三条曲线离得非常近,工艺角的影响小于温度的影响,我不信,仔细一看,是跑了MOS管的工艺角,见过国内有论文也这样搞的,根本就不对。

影响初始精度的还有op的失调电压和电流镜的mismatch

我弄了个东西,在不同工艺角下,温度特性曲线可以比较接近,但是温度特性变差了,但是将来所有芯片的偏差应该会有所改善

这个也不是我的课题,平时没事干,在驾校学车,想了个idea,居然还行,原来想写个论文,评奖学金用,初稿写好让导师看了,他语重心长地说不行,要申请专利,结果就改写专利申请书了

也不知道这个东西有没有实际意义,一般那些精度好一点的bandgap都要trimming的

小编最好给偶加个精华贴吧,最近没有分了,谢谢啦

1

2

3

目前好多产品的initial accuracy都在0.1%,不过比较贵

不清楚他们具体怎么做的

我猜大概是bipolar/BiCMOS工艺,再配合上laser trimming

模拟这东西,没有工艺支持,搞不好啊

怎么都没人回复啊,做过bandgap的兄弟给指点一下吧

bandgap应该是很通用的module

没有tapeout的经验,痛苦啊

模拟结果和测试结果确实是会差别很大的

如果工艺角,失调失配都考虑到的话

也会有很大差别吗?

差别会非常大的,如果是bipolar工艺做的话还好说,初始精度可以做到+/-6mV以内,但是如果是cmos的话除非用switch cap电路把OP的失调消除,否则是无论如何都不会达到这个精度的。

我主要针对的是工艺偏差,而失调是芯片内部不对称不匹配引起

我指的工艺偏差是指大批量产时,芯片于芯片间的离散程度

主要是因为

(1)同一个wafer上不同位置的die

(2)同一批次中不同wafer上die

(3)不同批次中的die

工艺稳定会影响bandgap的初始精度

这方面主要关系到器件参数

(1)电阻绝对值的精度 约+/- 20%

(2)pn结电压等

这些其实受工艺决定,比如doping density ,the depth of difussion,

doping profile 等

仿真结果没什么意义,古老的方法都是激光修调,现在一般都是通过一个数字电路调电阻网络

还有一下比如说存储电荷的方法

0.35um CMOS的bandgap (Vbe 用PNP 做)

case 1: process:ss avdd=3.0 temp=100

case 2: process:ff avdd=3.6 temp=-40

結果差異不大 1.217 +/- 1mv

OP是self bias 所以沒有bias issue

至於current mirror layout mismatch 因為通常是

designer 自己handle layout. 誤差是會有的. 但不會很大

为什么FF SS corner 均大于TT呢?

为什么ff 和ss corner 都比tt 的时候大呢?不是一般应该介于tt的两边么?

这种情况适合model有关么?不解,希望哪位能解释一下?谢谢啦!

您好!不知道您用什么工艺库跑的

我感觉你跑的不对!我在前面的文章中就已经提到过

CMOS的bandgap的关键是在 (用PNP 做Vbe)bjt的工艺叫,

而不是mos的工艺角!

pn结也是有工艺角的,电阻也是有工艺角的

mos管的五工艺角基本不影响bandgap!

就是因为我要补偿工艺角的影响,用了新的结构,结果就弄成这样子了

是优化的结果

good talk

我做了一款芯片,量产后测试发现bandgap的温度曲线顶点漂了很多

设计时大概在30度左右,tapeout后做温度测试发现竟然到了90度

bjt的影响小于cmos process corner的影响吧 个人看法

似乎对于简单的结构来说 corner的影响是不可避免的

对与顶点飘溢的影响 也比较常见 我个人也不知道原因 但是熟悉工艺之后 你就会把握好这个提前量了 可以把拐点提前改变

为了得到高精度 就得采取复杂的结构

no tapeout, no sense

Moreover, it can hardly find the advantage from simulation result.

It is easy to achieve the SPEC.

像楼上说的那样,高精度的bgr都是需要非常昂贵的trim,用来调整那个resistor matix.

用数字电路调电阻是什么意思?

全跑corners, 如果是biCMOS的工艺

pmos,nmos(f,typ,s),bjt,r,c(h.typ,l),temp(min, typ, max)

排列下来至少是50~60个,全面的会跑道1~200个左右

很多国内专利,paper都只能当绪论看看,就是这么来的

没有流片,没有真相, JSSC的论文基本上都会秀一下芯片照片,加上测试数据.

BANDGAP性能是和工艺结合得很紧密的,仿真不能体现出所有的问题,(model不总是那么可靠的);

triming见过的有三种:1传统的熔丝,(分为poly 和metal),优点是便宜适合少量的trimming,缺点是:需要PAD,占用面积大,数量多了就不可行了

2 激光烧短,优点是:占用很少的面积,可以实现更多的trimming 缺点是:需要工艺支持,另外CP时也需要专门的设备,贵!

3 利用OTP或者EEPROM,结合数字电路进行trimming.优点:可以实现封装后trimming,减小封装漂移,适合需要较多trimming的IC.缺点:需要工艺支持,电路设计更加复杂.

如果是非常有创意的想法的话,还是多做些功课, 想办法搭MPW流片吧(便宜些).

我主要针对的是工艺偏差,而失调是芯片内部不对称不匹配引起

我指的工艺偏差是指大批量产时,芯片于芯片间的离散程度

主要是因为

(1)同一个wafer上不同位置的die

(2)同一批次中不同wafer上die

(3)不同批次中的die

工艺稳定会影响bandgap的初始精度

这方面主要关系到器件参数

(1)电阻绝对值的精度 约+/- 20%

(2)pn结电压等

这些其实受工艺决定,比如doping density ,the depth of difussion,

doping profile 等

mark 。这样的方法后来再用过吗

我最近也在想这个问题,就是那个最常用简单的带隙结构,后来我想了想,那个vbe电压在corner下变化会变得很大,有40mv的误差,后来单独仿真管子,和仿真带隙基准,发现的结过时,在corner下,输出电压有40mv的变化,而管子单独仿真也有40mv的变化。最后能够将这种误差减小。

1.

有些

process 会提供

mismatchmodel 可以先跑monte carlo , 考虑process 分步但是

准不准

?

2.

bandgap 一般差异是

bjt造成deltavbe 其实比较小

, 反而是cmos 不论op_amp 或是

cmoscascade 都使用mos 放大

光mos delta_vth 偏差就是影响主因之一

, 电阻同type可以cancel掉

但是如果考虑温度会使用不同type电阻但是有时修不了

还有一类使用

低温度系数电阻

3.

量产来除非要求

-40~125度

要求很小

, 但一般是希望

die-to-die,

wafer-to-wafer 良率可以而且生产来说不太会使用温度只有初期会自己测, 如果有lasertrim 一般都设计可以修正, 另外package 后bandgap 电压会因为封装应力或stress有几mv差异

如果要求

bandgap是1mv有些会使用

effuse做PACKAGEtrim 方式

.

4.

model 温度参数对bjt来说都太少

cmos process下bjt model 都很”简略” 你自己看spicemodel 就知道

加上bandgap有些使用bjt是寄生

也是一个问题

5.

一般cmos 来说

拿bandgap做clock可以2%但是要做到paper提很低ppm实际上不多吧

因为spice model 本身对温度

-40~125

但有些设计是要150度下

.

另外好像目前有些人设计是

trim free,

至少die上看不到

laser fuse , 有没有efuse 就不知道

, 但是一般efuse要烧poly须大电流得一次烧断否则poly会变大阻抗, EFUSE如果使用metal须要更大电流

但又得小心metalfuse不会蚀刻断 (一般都违法drc rule)

有没有人设计过

trim free 的badnagp ?

以前测过

量产bandgap 温度差异

spice simulation 跟量到是完全不相同方式

但代工厂说已经新model

以前测过

量产bandgap 温度差异

spice simulation 跟量到是完全不相同方式

但代工厂说已经新model

这种bandgap,BJT/Res的corner影响才是最大的,MOS管corner的影响肯定在+/-5mV.

除了特殊工艺,肯定需要efuse或者laser trimming的

mark

bandgap确实需要看工艺,还有结构的。

看小编的帖子,应该是CMOS工艺。如果考虑mismatch,需要工艺库有mismatch的描述才可以有用

corner的误差,可以通过Trim解决的。

marking

一般来说补偿不了的。补偿了这个,就会带进去那个,总误差很难减小。

mark:)