cadence标准库中理想switch元件仿真问题

时间:10-02

整理:3721RD

点击:

第一次仿真理想switch,在仿真cadence标准库里面的switch元件时遇到了问题。

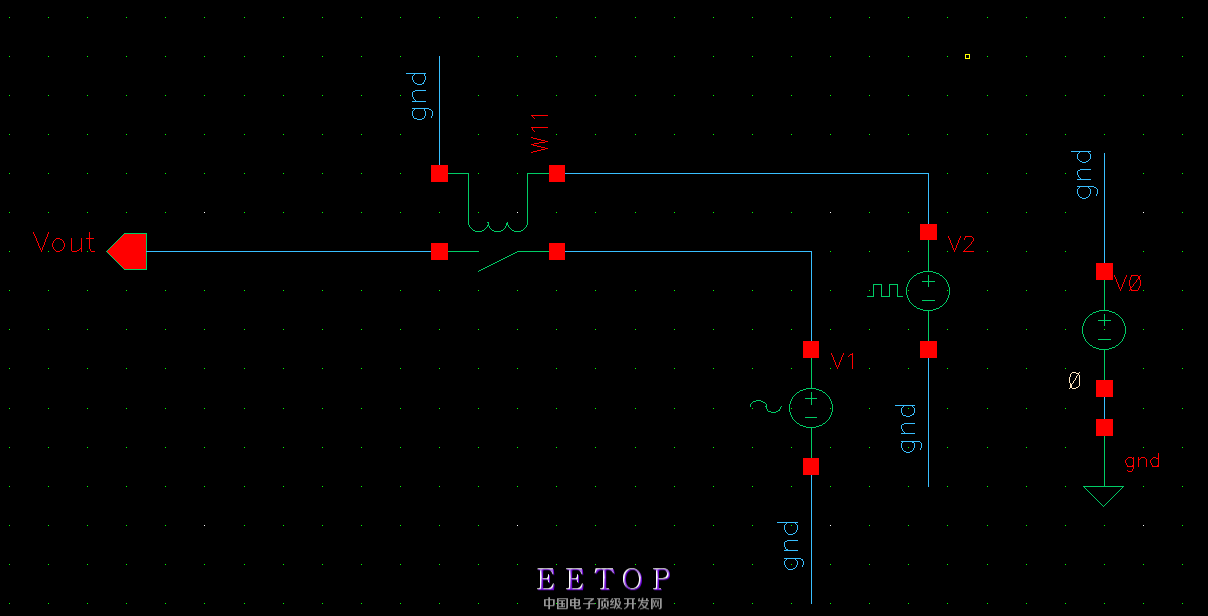

下面是我搭建的电路图:

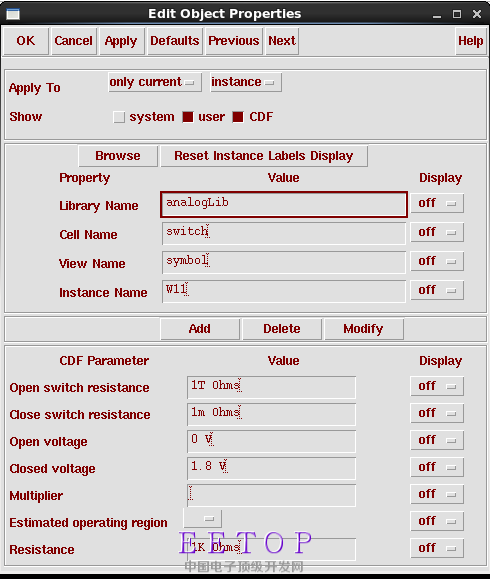

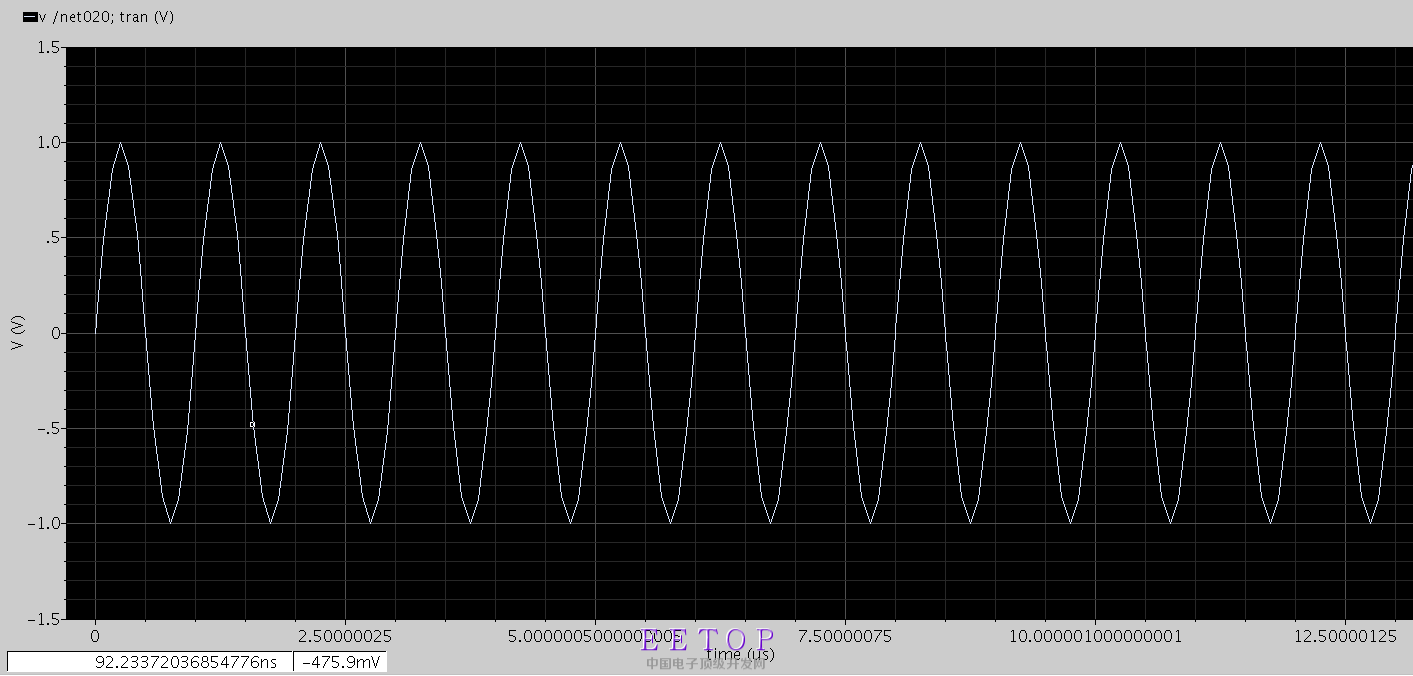

switch设置、控制方波信号和要传输的正弦信号如下:

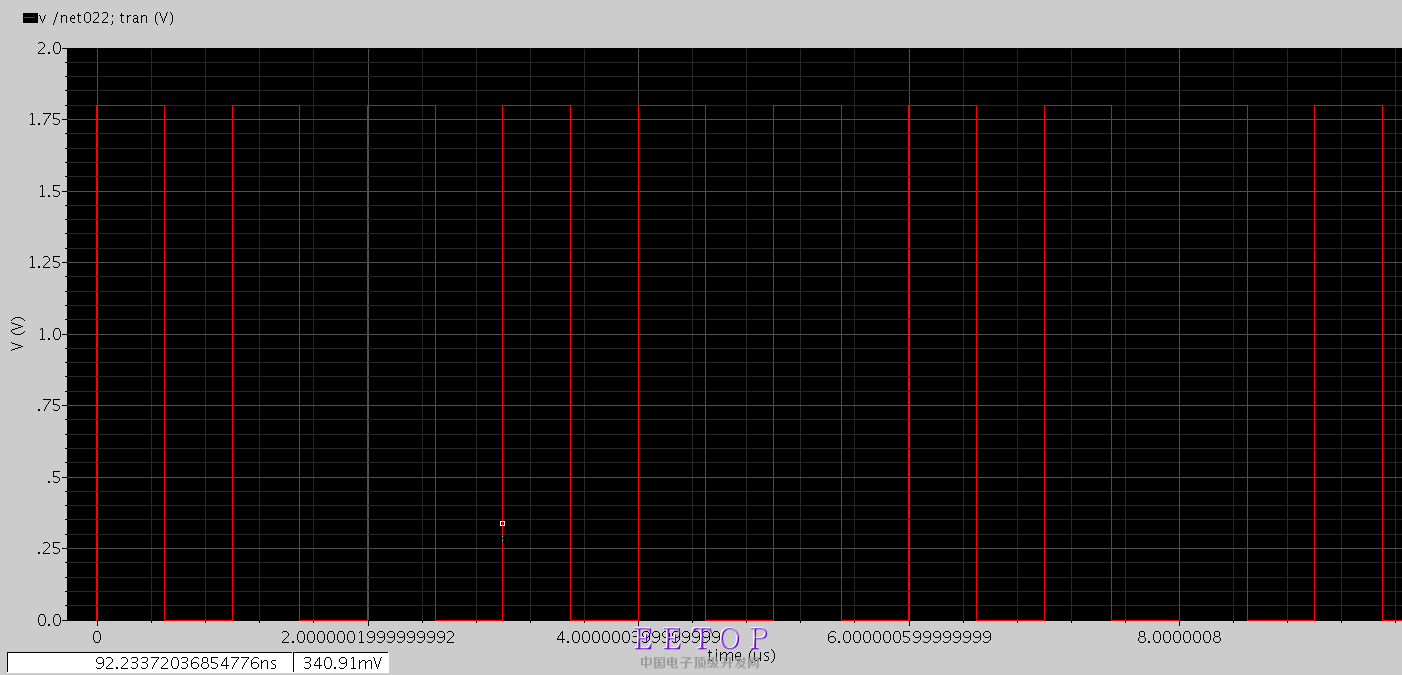

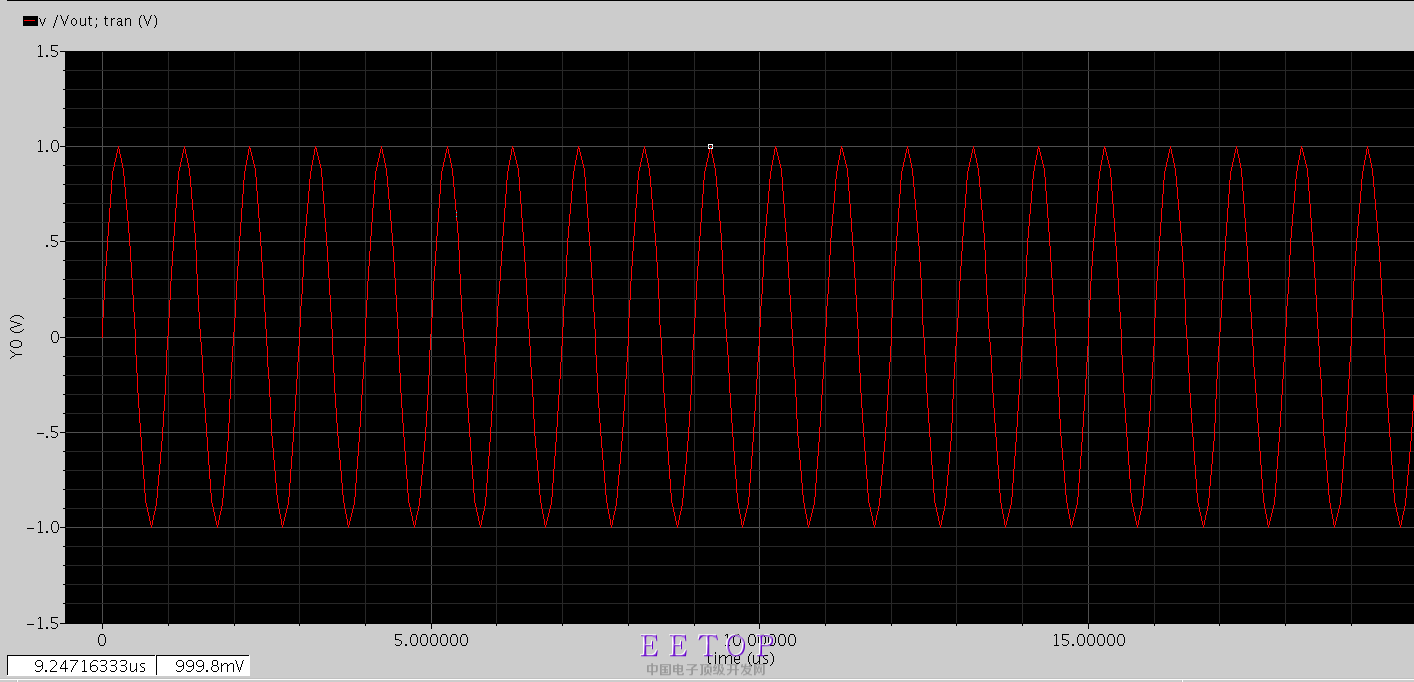

Vout端输出信号如下:

开关并没有出现方波为1.8V时导通,0V时截止的情况,而是一直都处于导通状态,请问有大神知道是什么原因吗?

没有大神知道吗?求帮忙啊。

Thanks for your sharing!

把最后一行的“Resistance”改为1G。

选用symbol,然后在Vout端串接电容就可以了。

谢谢你的回复,好的,我试试看。

感谢你的回复,我明天开服务器试试看。

最后一行的resistance换成1G也不行,在analogLib选器件时,view我选的cdsSpice解决了。请问最后一行的resistance代表什么意思呢?

谢谢你的回复。输出端传戒电容也不行,在analogLib选器件时,view我选的cdsSpice解决了。

6666666666

我曾经碰到过跟你一样的问题,后来解决的方法是在输出端串接一个1PF的电容,switch参数设置为Open resistance 1T ohm,Close Resistance:1 ohm。我的理解如下:相比ahdlLib库中的SW元件,AnalogLib库中的switch元件更符合实际情况,因为实际用开关的时候是要考虑自身导通电阻与负载电容的,所以开关输出端需要接一电容负载。不知道我的理解对不对?

嗯嗯,赞同你的观点。

修改下close voltage和open voltage?这么正好是gnd和vdd的话不知道会不会有问题。