veriloga 积分函数idt相关问题

时间:10-02

整理:3721RD

点击:

求教各位大神:

1、idt函数的积分区间是怎么设置的?默认积分上限时间t是指哪个时间?

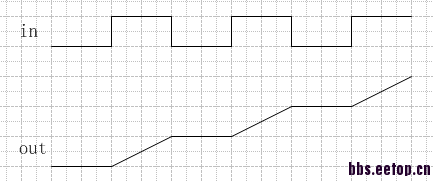

2、有资料说idt之类的analog operator不能出现在if/case语句中,那么如何描述在某个脉宽范围内求积分(方波积分成三角波)?如下图所示:

3、analog begin

@(cross(V(v1_1)-1,+1)) begin

V(v3)<+ idt(V(v1),0);

V(v3_1)<+ V(v1);

end

vx= idt(V(v1),0);

V(v4)<+ vx;

V(v5)<+ ddt(V(v1));

V(v4_1)<+ V(v1);

end

为何这边的微分正确,积分得不到正确的结果?仿真发现对输入任何波形积分,输出都为有一定斜率的斜线。

4、veriloga中能否对时间进行操作,比如在输入信号高脉冲时间,输出信号持续近似线性增大?(比如又区间范围的积分?)

1、idt函数的积分区间是怎么设置的?默认积分上限时间t是指哪个时间?

2、有资料说idt之类的analog operator不能出现在if/case语句中,那么如何描述在某个脉宽范围内求积分(方波积分成三角波)?如下图所示:

3、analog begin

@(cross(V(v1_1)-1,+1)) begin

V(v3)<+ idt(V(v1),0);

V(v3_1)<+ V(v1);

end

vx= idt(V(v1),0);

V(v4)<+ vx;

V(v5)<+ ddt(V(v1));

V(v4_1)<+ V(v1);

end

为何这边的微分正确,积分得不到正确的结果?仿真发现对输入任何波形积分,输出都为有一定斜率的斜线。

4、veriloga中能否对时间进行操作,比如在输入信号高脉冲时间,输出信号持续近似线性增大?(比如又区间范围的积分?)

fig. 01

目前发现了问题,电压积分是有最小step限制的,如果积分值过小,积分曲线就会出错,但最终值正确。可以将积分后的值放大就可以看到正确的积分曲线。

另外一个问题,hsim仿真idt函数为什么会有最小step限制。 可以调节吗?

我用过verilogA写运放,搭建一个基本的RC有源积分电路,给一个占空比50的方波,输出电压一直在上升。并不想输出的三角波那样。