LDO设计的几个问题

在做一个LDO,因为供电的片子功耗很低,正常是150uA,处理的也是低频信号,碰到几个问题,还望做过的前辈们不吝指教下。

1,调整管的问题

后面的供电模块工作电流是150uA,因为后续版本可能加入其他的电路模块,所以负责人说让我最大电流假设到1mA。于是我按照最大电流1mA下管子工作在饱和区,计算了调整管的尺寸。但是后来发现,负载变为150uA的时候,调整管工作在了亚阈值区。所以想问一下,调整管这种情况电路能正常吗?看已有的原理分析,在整个电流范围内,管子都应该在饱和区。

2,环路的稳定性

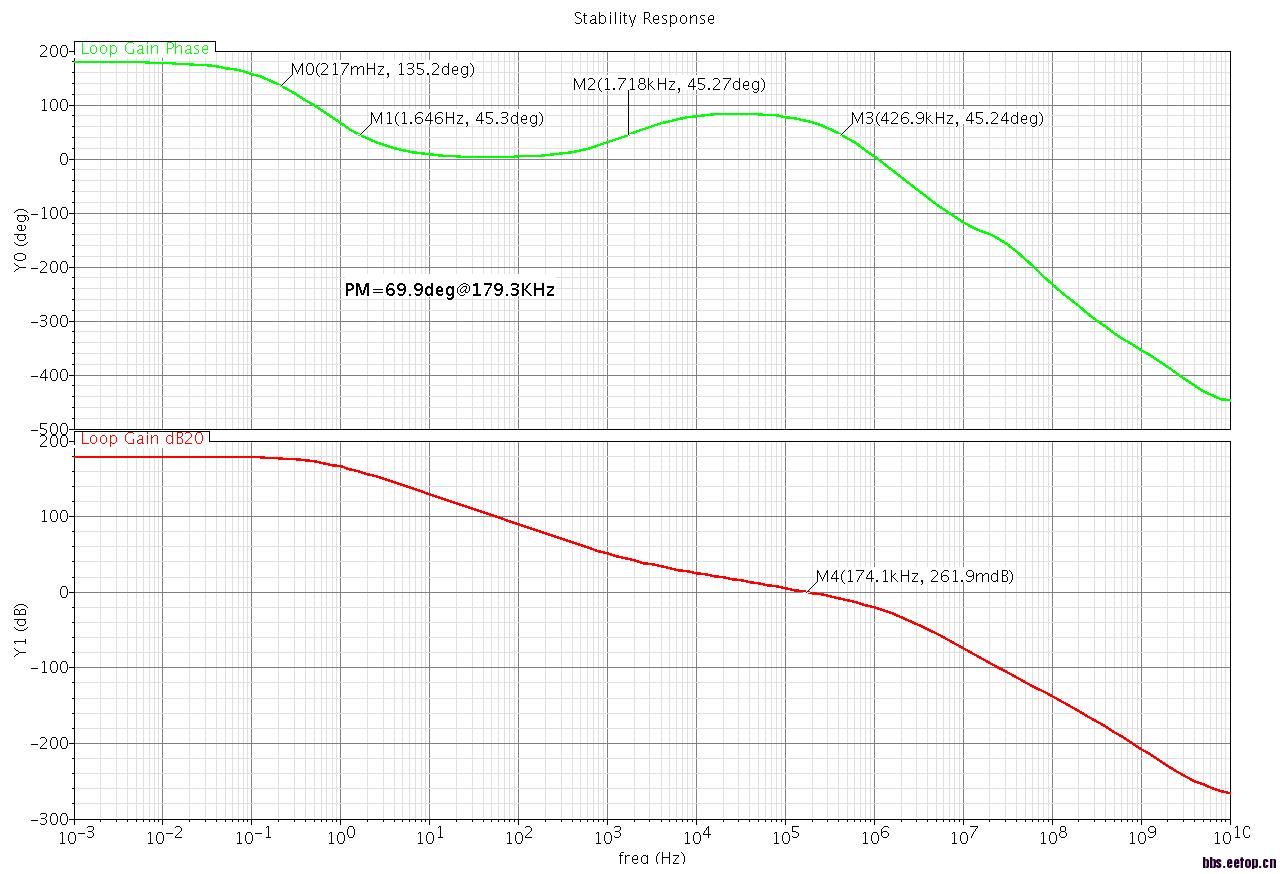

输出电路是4.7u,输出旁路电容式10n,加了一个20ohm的ESR电阻仿真,相位裕度是够了。但是这个20ohm的补偿电阻是不是值大了些?然后导致瞬态特性变差,过冲的峰值过大。

另外一个问题是,我分别仿了空载,150uA,1mA三种负载情况的相位裕度,发现150uA时的PM最大。但是看paper后理解的应该电流越大,相位裕度越好才是。

第三是,看相位响应图,我判断不了主极点到底是在输出端还是在误差放大器的输出端,按照P1=1/2pi*Ropass*CL; P2=1/2pi*Resr*Cb; P3=1/2pi*Roa*Cpar,算出来的数值和曲线上看到的不大一样,除了P2这个高频极点能分辨的出来外,前两个极点都挨的特别近,附图是负载为1mA时候的图。不知道误差运放的输出阻抗Roa怎么算,所以我现在都判断不出来主极点是哪一个。

看了很多已有的LDO的设计,都针对的是几百mA,最小也是十mA负载的设计,而且应用的也是高频领域,对带宽的要求比较高。而我现在做的是低频的应用,对带宽的要求应该特别低,而且电流这么小,刚开始的时候觉得应该是很好做才是,但是现在发现这几个问题都好奇怪。想了好几天都没有很好地解决。

希望大伙能给点建议,是不是无电容型的结构会更加适用一些呢?

看了小编的描述,选用的LDO似乎是经典的LDO结构。根据某文章的分析,在0~1mA之间的稳定性是不太容易做的。根据你的提问,给写愚见吧,呵呵

1、调整管的工作区域:一般经典LDO结构,要求工作在饱和区。但是也有列外的,比如2003JSSC的一篇(香港大学)DFC型的LDO,调整管是可以工作于线性区的;工作到亚阈区的也有,记不清是哪片文章了,似乎是2005年的一片微分器型LDO中有讲到。

2、环路的稳定性:经典LDO结构的频率补偿,通常要Cout加上小的ESR,ESR似乎不要超过10ohm。其实这里我也有个疑问:为什么要加10n的旁路电容,要知道,他和ESR结合,会产生新的极点。一般文章里分析时,这个旁路电容指的是供电线的寄生电容。

从你的描述来看,主极点似乎仍在输出端。输出电阻的计算很多paper里都有讲到哦,呵呵。耐心细致就能找到答案了。LDO的带宽一般在几百K左右。

呵呵,其实坛子里有很多paper 的。我从不知LDO为何物开始,在坛子里下了很多的资料看。从简单到复杂,呵呵。现在还有很多东西仍在学习中,但大概知道LDO为何物了,呵呵

其实,我可以针对性的给你几篇文章,但是服务器不支持上传,我可以晚上回家发给你。留个邮箱吧

这么小的负载能力,完全可以做无外接负载电容结构,第一个问题,pass管工作在什么状态并不重要,重要的是在各种条件下pass管能提供最大负载电流就行;第二个问题,主极点在输出处,当150uA负载时的主极点相比1mA负载时更靠原远点,故相位裕度更好

如楼上所说,这么小的负载能力,完全可以用片内电容实现,也不需要很大的面积。觉得在150uA的情况下最好是让管子工作在饱和区,这是你的常用负载。负载能力比较小,调整管的w不用弄的很大,那么在150uA饱和应当不难。一般,负载小调整管才会在线性区,负载大的时候很容易会在饱和区的。

嗯,手上有那篇paper。其实现在手头上LDO方面的paper有好多好多,但是就像这篇一样,基本都是针对重负载的,所以引用过来的时候总有很多问题。你说的对,耐心细致总会解决问题的。我的邮箱2006mizi@163.com谢谢这位童鞋了~

才1mA的最大输出电流,做什么片下电容,最简单的LDO结构都搞定了...晕

嗯,有打算设计无外接电容型的结构。如你所说,电流小时输出极点更靠近原点,故相位裕度更好。那为何负载电流为零时的相位裕度相对150uA时又下降了呢?

电流大更容易工作在饱和区没有错,可是如果管子尺寸是按照150u计算设计的,那么1mA负载的时候,调整管在饱和区,但是Vdsat会增大,dropout电压就变大了,效率也就低了。

是的,我目前只是采用了最最最简单的经典结构,零极点的分析也是参考Ricon-Mora的那片博士论文学习的。因为记了笔记,看别的文章里说过,旁路电容Cb有个作用是减小瞬态特性里的那个delta Vesr的影响。不是非常地清楚,旁路电容基本就是滤波的作用,既然有输出电容了,再加旁路电容看着好像是有些多此一举

150uA到1mA的跨度并不大,dropout其实并不会有什么变化的;变化的大,那也就是调整管没有设计好。负载小,假如用很大的调整管,那就浪费面积了。

学习了~

如果你采用的是一级的运放结构,只要在取样电路中加入补偿电路即可实现稳定

如果采用两级运放,对于你的负载波动范围小,也可以通过在取样电路中选取合适的补偿就可实现稳定。

如果问题没解决,你可以把图上传到网上让大家帮忙分析分析

上图吧,这样清楚一点

我觉得你这个完全可以做个一级放大器+buffer驱动输出mos管,之后加些片上的电容做负载,就应该能满足一般的瞬态响应了。补偿用输出极点作为主极点,之后把放大器和buffer之间的极点,buffer和输出管的极点 都移到带宽之外。如果有困难,可以在第一个反馈电阻上并一个电容,做个零极点补偿。

毕竟你的这个电流范围很小,不会太复杂的,另外160uA的静态电流太大了,完全可以做到更低。

既然你手上有好多paper,看下有没有这篇:A Capacitor_less Low Drop-out Voltage Regulator with fast Transient Response(2005Master Thesis, by Rebert Jon Milliken_Texas A&M University)和这篇Full On-Chip CMOS Low-Dropout Voltage Regulator(2007IEEE, by Robert J. Milliken等)。其实这两篇讲的是同一个电路,可以参考下,负载电流在0~1mA,这个电路是可以稳定的。

经典LDO在这个负载电流区间的稳定性似乎有点困难,原因是传输管的gm小。愚见!

好

求资料 万谢 zhengjinlong1988@126.com

学习了

不错!

关于Bypass Capacitor的作用是减小瞬态特性的问题:瞬态特性是指:当负载电流发生突变时,引起的输出电压最大的变化,也称为过冲,

一个LDO对于电流的变化的响应公式为:

deta-V-trans=I0-max*deta-t/(C0+Cb)+deta-V-esr

旁路电容使输出电容的等效并联电容增大,从而减小了电容产生的过冲,因此可以改善瞬态效应

seeing

您好,请问能给我发几篇文章吗? 我遇到了LDO在空载(8uA)到100uA之间,环路不稳定请指点

你好,能不能麻烦你讲一下,第一个反馈电阻并联一个电容,然后他们在串联一个电阻回到误差负输入端,能说一下这种补偿的原理吗

请问ldo设计时,输出负载电容为1nF,负载电流从0~100mA跳变,有没有好的电路参考。