EE240 2006 第四节课的一个电路,为何我仿真的不收敛(有图)

时间:10-02

整理:3721RD

点击:

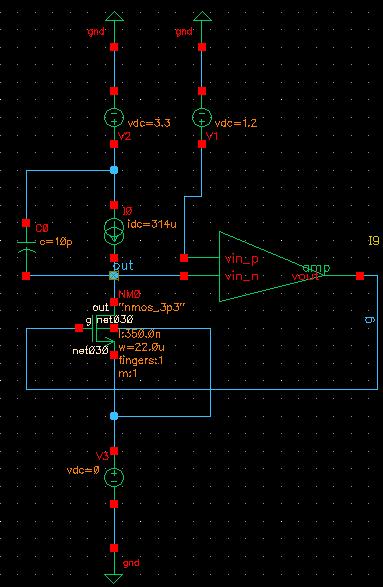

如图,运放为理想运放。

仿真错误提示:

Error found by spectre during DC analysis `dcOp'.

Matrix is singular (detected at `out' and `g').

No DC solution found (no convergence).

The values for those nodes that did not converge on the last Newton iteration

are given below.Also given is the manner in which the convergence

criteria were not satisfied in the following form:

Failed test: | Value | > RelTol*Ref + AbsTol

I(I9:vout_flow) = 0 A

residue too large: | 1.2 V | > 6 mV + 1 uV

V(net034) = 0 V

residue too large: | -314 uA | > 1.57 uA + 1 pA

V(out) = 0 V

residue too large: | 314 uA | > 1.57 uA + 1 pA

顺便说一下,EE240 2006 为一美国口音老外讲授,比bosor容易听懂,但好像没他详细

仿真错误提示:

Error found by spectre during DC analysis `dcOp'.

Matrix is singular (detected at `out' and `g').

No DC solution found (no convergence).

The values for those nodes that did not converge on the last Newton iteration

are given below.Also given is the manner in which the convergence

criteria were not satisfied in the following form:

Failed test: | Value | > RelTol*Ref + AbsTol

I(I9:vout_flow) = 0 A

residue too large: | 1.2 V | > 6 mV + 1 uV

V(net034) = 0 V

residue too large: | -314 uA | > 1.57 uA + 1 pA

V(out) = 0 V

residue too large: | 314 uA | > 1.57 uA + 1 pA

顺便说一下,EE240 2006 为一美国口音老外讲授,比bosor容易听懂,但好像没他详细

1. 為何vn端 還要串一個current ?

vn端應該是個high Res , 你加電流也沒用阿 ..

2. 你的op 掌怎樣 ?

從你的訊息看起來應該是你外接的東西造成的才對 ..

电源和地衣这种方式给出看起来好费劲阿。是不是运放接反了?貌似直流正反馈。你的运放用的ahdl?

运放接反了

的确接反了

首先检查Op正负极性问题

另外要注意得是

在该试验中,Op的放大倍数不可太大

Av=100左右就可以了

过大的话仿真会有收敛性的问题

Nak教授在上课时说明了这一点

thx,正需要

学习了,感谢楼上的各位大神

小编可以把这个课的视频共享吗?非常感谢了,我在论坛找了好久没找到。

小编,能给个视频链接吗