运放型bandgap的启动问题(低电压结构)

时间:10-02

整理:3721RD

点击:

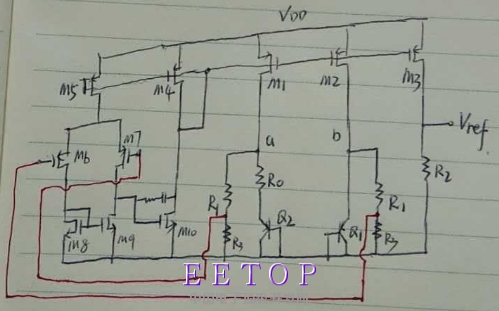

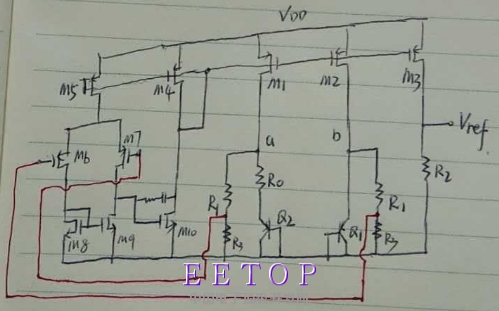

(1)如图所示,利用运放虚短虚断原理,可以求得带隙电压为:Vref=R2/R1 (Vbe+R1/R0 VTlnN),在DC情况下,我将Vref调成500mV了(2)但是有一个关键问题,上电时发现电路无法启动(VDD先上电,PowerDown信号后上电),求这种带隙的启动电路推荐!

感激不尽

感激不尽

我尝试过opamp电流采用自偏置,而不是由带隙提供,这样的话op也要一个启动电路,带隙core也要一个启动电路。还是不能起来~

要两个启动电路的话,感觉启动有个先后顺序,还不如用图示结构,但目前没找到合适的启动电路,求指导~

自己顶一下

sansen 16章先过一遍吧。1640那张图就是

1640那个,是不是运放也加了启动,如果op没起来,即使反相输入端电压>同相,输出也没办法被拉低吧!

这种结构论坛里有分享的资料,大概思想就是通过上电时拉高M10 gate电压,导通M4

谢谢~我试试!

很有用。 谢谢。

做过一次sansen里边的那种结构,运放如果建立慢的话,启动电路关闭的时候运放还没建立完,三极管上方的管子是无法提供电流的,试了一下更改启动关闭的参考点,将PMOS的栅极与VB相连,如果运放没建立,PMOS栅极是高电位,启动电路不关闭,直到运放正常工作为止。PS:只知道启动电路在正常工作后应该彻底关闭,不知道还有其他什么要考虑的。

把M10的栅压拉高这种启动很有用的,我已经在全工艺角下可以启动了,而且挺快的。

运放 gain 很高 没有起动电路 bandgap 还是会动作 , 但是 流片是有 > 20% yield loss-> 前人设计失误 .

hspice 完全模拟都会动作 , 量产也会动.

但是流片大量 时发现出问题 .

你其实可以拿 vref去控制 NMOS ,

vref < vth 下 start up 动作

当 vref > Vth 关掉 start up . 不过某些情况下可能会 "ring" 就是 start-up circuit 开开关关 .