求助:高速CML驱动器的波形经过变压器后共模异常下降

时间:10-02

整理:3721RD

点击:

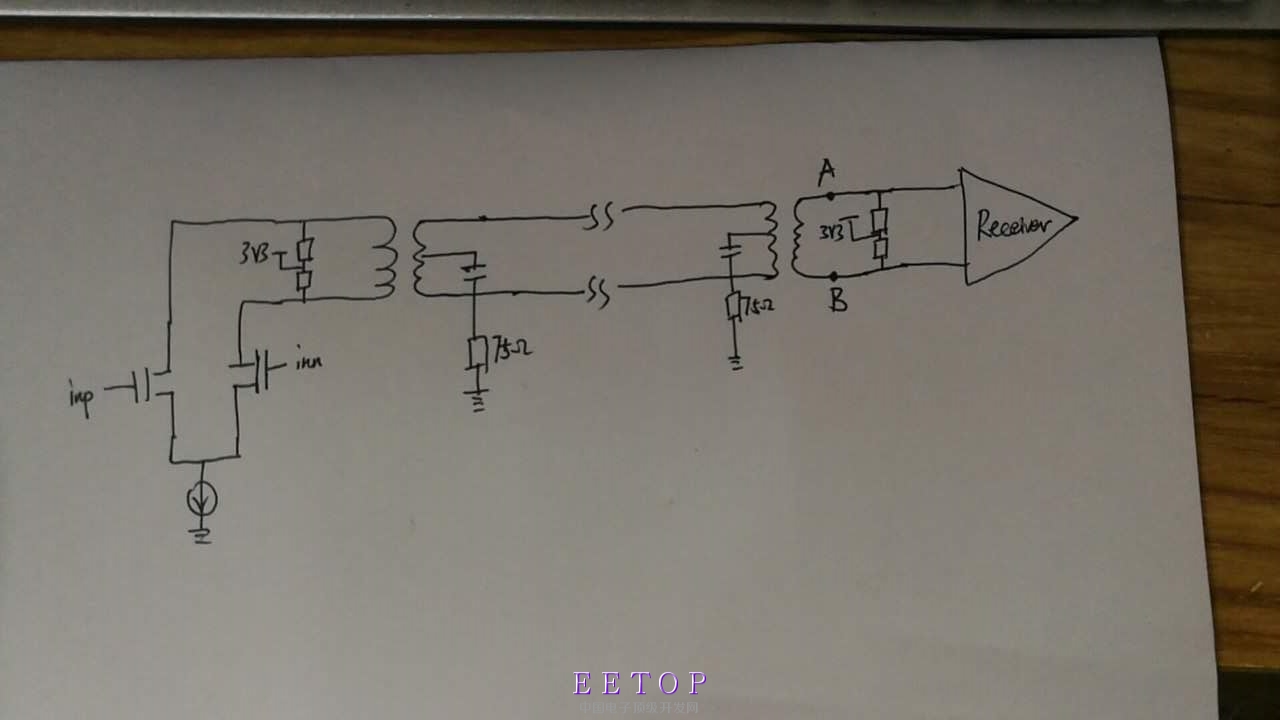

最近设计了一颗高速数据传输的芯片,用的CML结构的驱动器,用5类双绞线做介质,变压器耦合。传输600Mbps的差分信号。芯片回来测试后发现,在接收端,经过两个变压器之后的信号,就是图中AB两点,每个数据包开始后共模电压都会缓缓下降,非常奇怪。请教一下各位前辈,这个是什么原因?如何消除?

下面是电路图:

波形如下:

其中,空闲时,共模被VCC拉在3.3V上,理论上,当信号过来后,差分波形应该以3.3V为中心上下摆动,但是实测发现波形会缓缓下降,当数据包结束时,再回到3.3V。感觉非常奇怪,希望各位前辈帮忙看一下原因,谢谢。

没有人回答吗?

自顶一波

猜测(1)变压器阻抗变化引起的,可以接收机前面的电阻阻值加大,共模工作点会下降。(2)由于接收机PAD的寄生电容和电感谐振产生的电阻进行了分压。以上只是猜测,我对变压器不熟,仅供参考。

谢谢