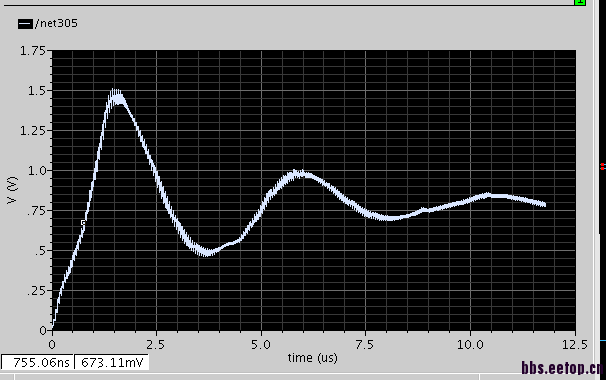

锁相环中VCO的控制电压有波纹

想问问这是由于什么原因导致的呢,是因为环路滤波器的参数设置的不好吗

[img][/img]

这是VCO控制电压的图片

VCO的干扰,,没事

那VCO的干扰可以从哪些方面降低呢

没有紋波拜不正常。

那纹波怎么可以尽可能减小呢

为什么要减低呢

因为VCO的控制电压最后稳定了,就代表环路锁定了吧,VCO的控制电压有纹波,感觉有谐波的影响,肯定是不好的,锁定最理想的情况就是VCO的控制电压是一个定值啊

要是没有所有的噪声和非理想性,那就是定值了,不过那样的话PLL就没有难度了。

如果这个文波和VCO同频呢

我假设你说的纹波是ripple,不是那个control voltage的transient response

如果你做过switching power supply的话,这个可以类比输出电压的纹波,是无法避免的,但的确有办法可以减小。

首先你得熟悉PLL的结构,假设你的PLL是charge pump type,那么每一个reference clock cycle,charge pump都会有current pulses inject 到 integrating capacitor里,这个充放电就导致了ripple, 注意即时在稳态下这个current pulse 仍然会存在,防止VCO drift away.

所以说通过增加capacitance,也就是减小filter BW,肯定对于这个ripple是有效的, 另外也可以减小charge pump的current. 具体的分析可以看拉扎维的书。 注意如果filter BW太小的话,一方面feedback loop 反应会很慢,另一方面会导致VCO phase noise attenuation 不够,自己权衡利弊

标题

防止driftaway怎么理解?

PFD/CP 一般会有一个dead zone,比方说10ps, 如果你的reference 和 VCO phase error < 10ps, PFD 是不会输出任何UP 或 DOWN 信号给 charge pump的,或者是PFD输出了一个narrow pulse,但是charge pump的switch来不及turn on/off, 这就意味着你的VCO Phase 可以 drift 10ps, 但是你也不会发现。

通过delay reset signal for PFD/CP, 你保证了minimum pulsewidth,这样即使是10ps的phase error,PLL现在也可以做出反应了,就防止了稳态时VCO在10ps以内来回drift (10ps只是一个例子)

很多资料都有讲这个,拉扎维的书有讲,还可以参见这个 http://ece.wpi.edu/analog/resources/PLLTutorialISSCC2004.pdf

感觉你懂得真多,谢谢

我看你提到了电荷泵的充放电会引起ripper,是因为充放电电流并不是完全匹配引起的,这样解释对吗?

我是觉得VCO的纹波可能有一部分原因是因为电荷泵充放电电流不匹配导致的,那纹波的频率是和参考频率一样,而最终稳定情况是VCO的频率经过分频器以后和参考频率一样,而分频器分频比除非为1,那么纹波的频率才和VCO一样。哎呀,我不懂,不过感觉你问的问题很高大上啊

如果是VCO震荡反馈或干扰的ripple,和VCO同频,对VCO没有noise影响。如果是CP或者其他一些因素引起的就影响VCO noise了。

你说的很对,mismatch是最常见的情况。

http://www.seas.ucla.edu/brweb/teaching/215C_W2013/PLLs.pdf拉扎维的这个课件还提到了skew,反正总而言之即使在稳态时也会有charge pump电流对电容进行充放电,从而导致纹波

你提到了即使在稳态的情况下也会有电荷泵的充放电,是因为在稳定情况下,即使鉴频鉴相器的参考信号和反馈信号同频同相,UP,DW信号也会产生窄的,重合的脉冲导致的吗?

谢谢。

对的

谢谢啦,还有一个问题,就是我看到别人的论文经常会提到锁相环失锁,什么情况下锁相环才会失锁?

VCO pull range是有限的通常来说,所以一旦你的frequency plan确定了,就是说你的ref clk, divider, VCO 都定了之后,ref clk出现一些漂移比方说从100MHz漂到了99MHz,VCO有可能到达频率的下限了,所以分频之后的频率无法到达99MHz,这时就失锁了。

失锁其实就是指的分频VCO和ref clk的相位没有锁住的情况,锁住的意思就是保持不变。有时在refclk突然变化时,VCO调整的这段时间也是失锁的

了解了,就是VCO的最大频率经过分频以后还是小于参考频率或者是VCO的最小频率经过分频以后还是大于参考频率就会失锁,那除了这两种情况,还有其他情况会导致失锁吗?另一个问题就是我看有人提到了Cycle slip,你懂是什么意思吗?

http://www.delroy.com/PLL_dir/FAQ/faq_cycle_slip.txt

这是我在网上找到的分析的最透彻的一篇,虽然不带图,但讲得非常清楚。

正如我前面提到的,失锁就是指fdiv和fref没有锁住,PLL的瞬态响应决定了失锁的时间。

PFD是可以保证relock的,因为它能判别frequency,单纯的PD则不行。不过如果PLL响应很慢,即使最终通过PFD relock,在这个过程中也已经错过了一些fref cycle,这就是cycle slip

太感谢啦

感觉你好厉害呀,我还有一个问题想问一下,即使环路滤波器各个参数的计算有什么参考依据吗

loop filter的设计各种书里面都会提到,我之前发的那些链接里也有详细的介绍。

总的来说要考虑你的application,比方说,你的PLL就是为了提供一个high quality/high frequency clock, 那么phase noise就是主要的考量,通过调节loop filter BW来最优化你的Phase noise;如果用在通信中,需要经常跳频,那还得考虑PLL瞬态响应,同样,loop filter BW, damping factor都会影响响应速度。根据自己的具体情况具体分析。

你提的问题都很到位的,思考的很细,几个问题我其实在以前做项目时也没有想清楚或是没碰到过,也就是上网查找资料,你的问题网上都能找到解答