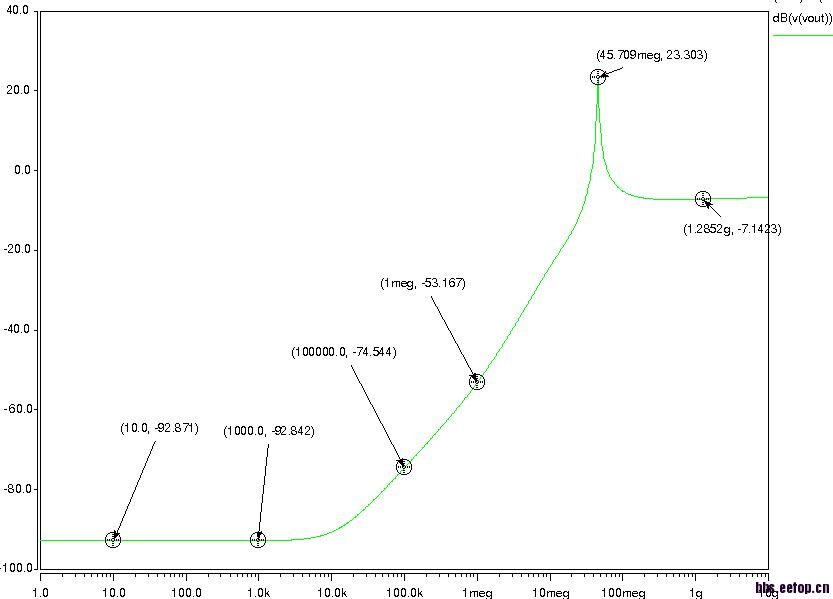

psrr 高频时>0dB

时间:10-02

整理:3721RD

点击:

大家好:

放大器的PSRR高频增益为正,不知是由什么原因引起,还请大家指导一下:

所以,当在电源上加上波动做瞬态仿真时,输出电压会冲到很高,

放大器的PSRR高频增益为正,不知是由什么原因引起,还请大家指导一下:

所以,当在电源上加上波动做瞬态仿真时,输出电压会冲到很高,

那一点不稳定?会起振?

谢谢您的回复。

还是不太懂,继续请教。

初步估计是环路增益随频率的减小快于电源到输出增益的减小,导致在某个频率下psrr大于0。检查极点位置设置。

超出环路的单位增益带宽的高频段,环路没有任何能力压制电源的抖动,这个时候的PSRR是由电源-放大器输出节点-地三个节点之间的电容分压决定的。所以用去耦合电容会有帮助,不过代价要考虑。

非常感谢您的回复。

但我认为,即便这三点之间的电容电阻分压,那也不可能有vout/vdd > 1 的情况出现的。

电容比为什么不可能倒过来?电源到输出点之间的电容大于输出电到地之间的电容就是这种情况. 在做电源管理模块LDO的时候,这种问题很常见,已经被分析的很清楚了.

如图:vout/vdd=(1/sc2)/(1/sc1 + 1/sc2) =c1/(c1+c2)<1,所以psrr<0dB

OK, 明白你的意思了. 你要看一下你的零点在哪里.

这个问题解决了吗?我现在的仿真也出现了PSRR大于0的情况,要怎么解决呢?