关于bg电阻trimming引起的PSRR下降问题

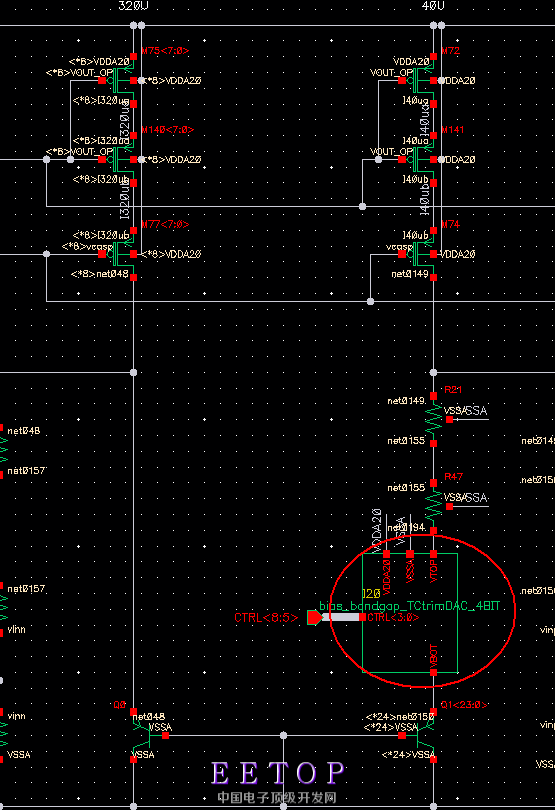

第一张图为bg的部分sch

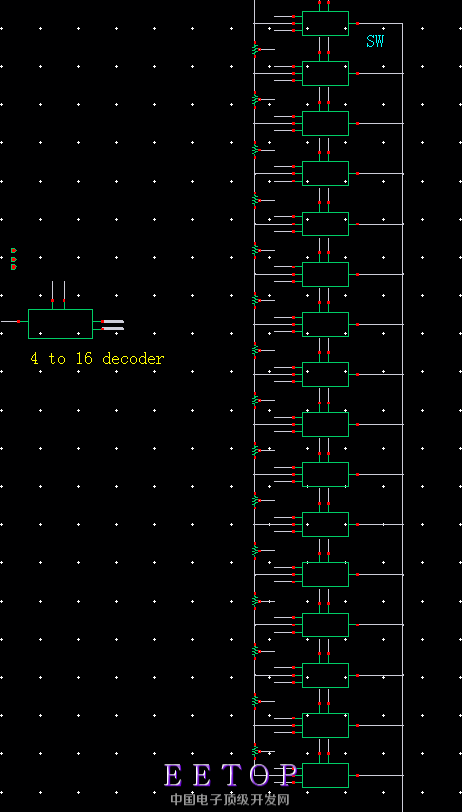

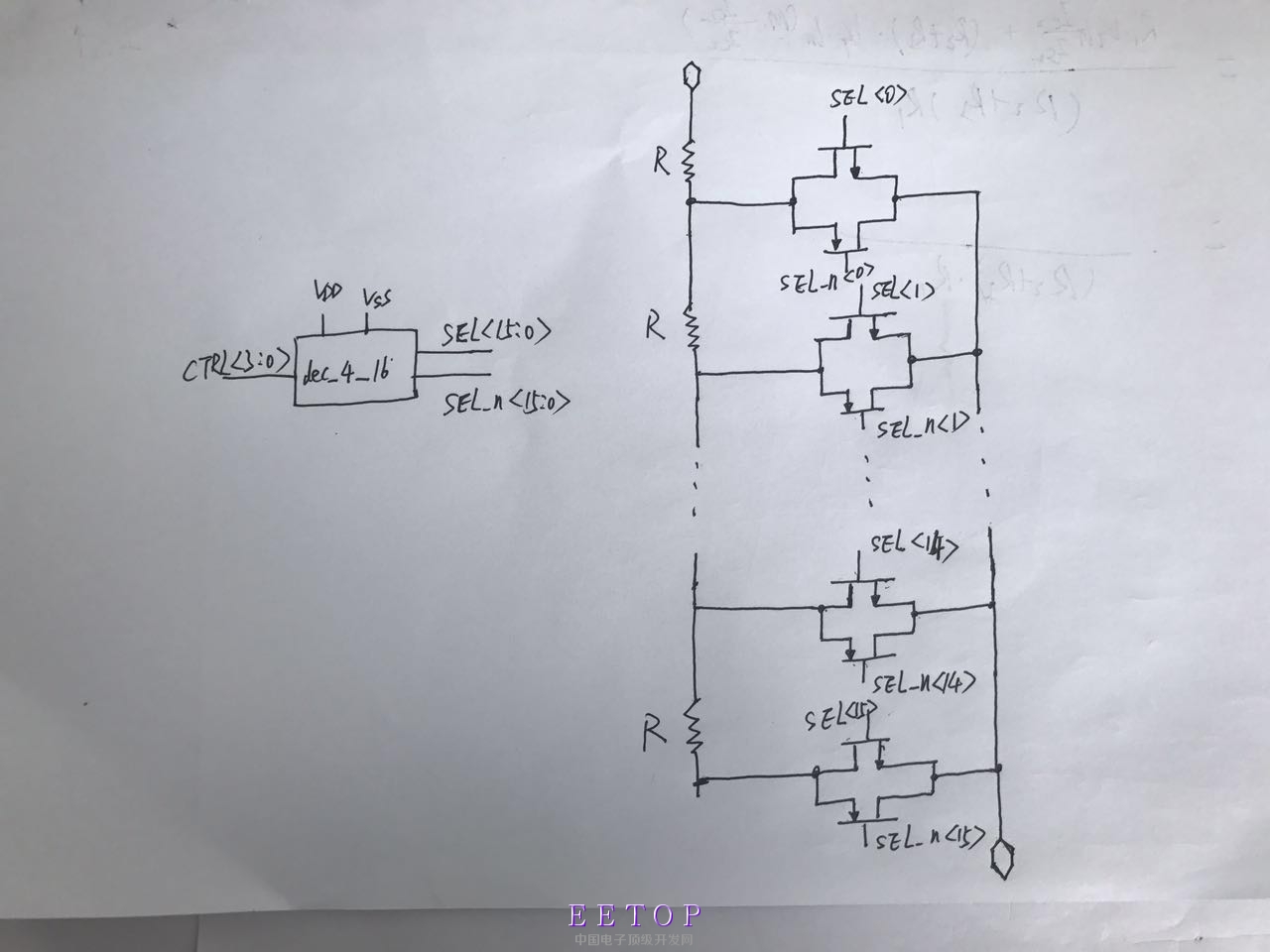

第二张图为trimming block内部sch

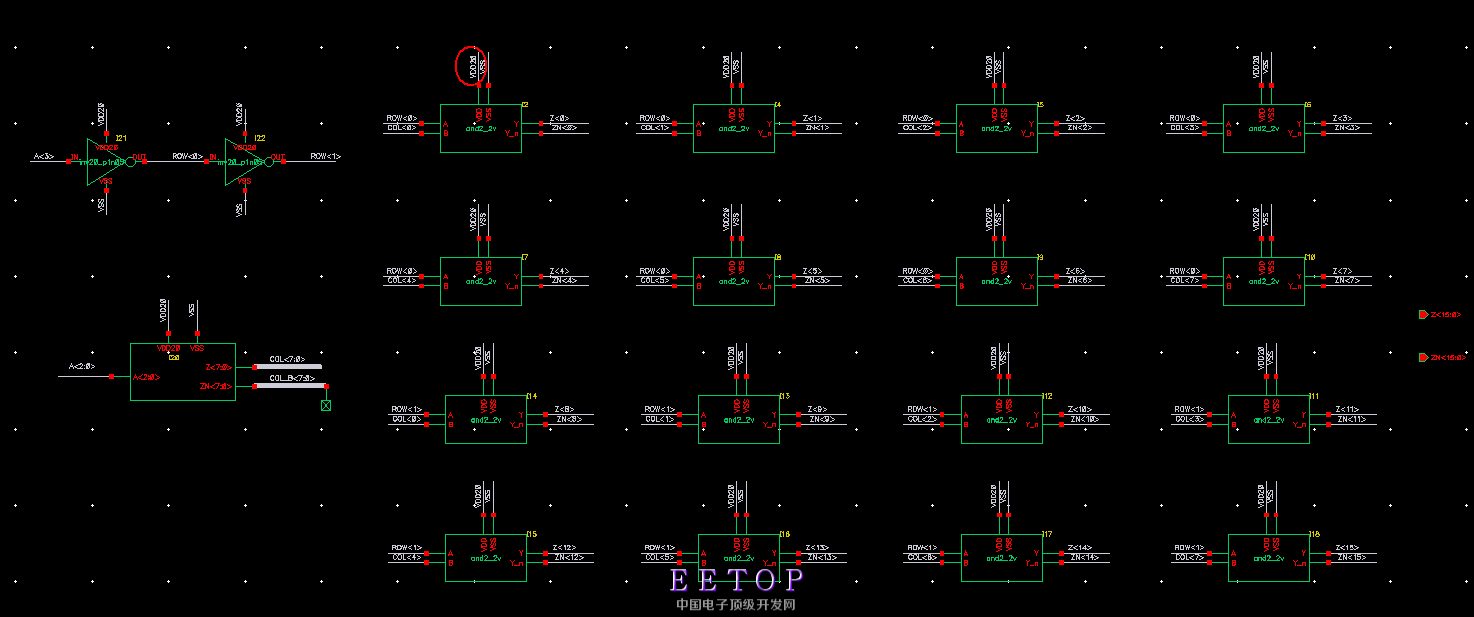

第三张图为4to16 decoder内部sch

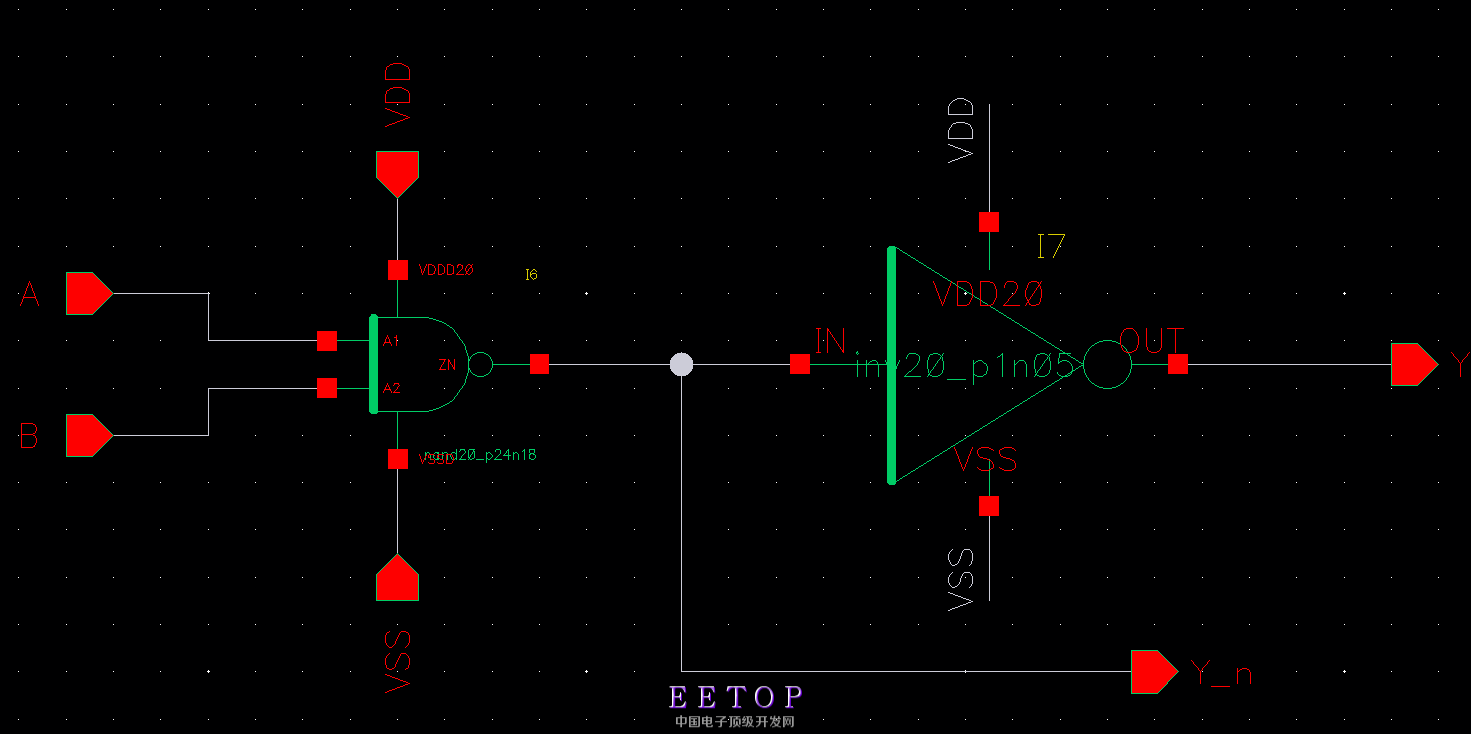

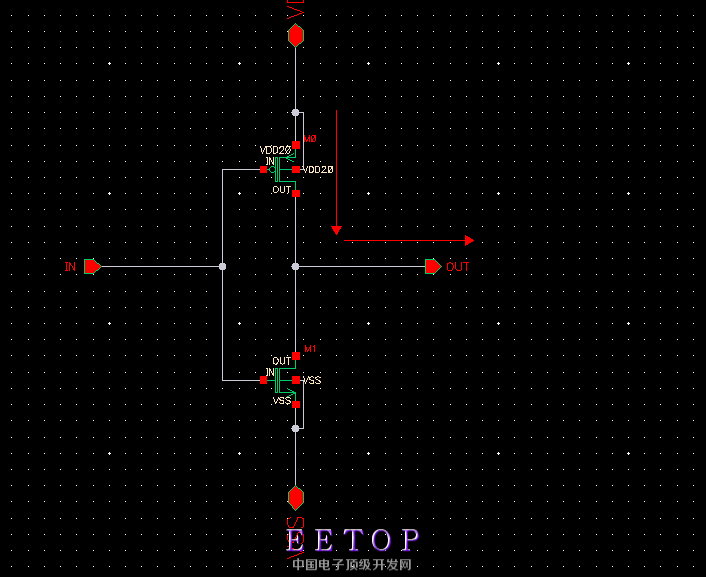

第四张图为与门内部sch

第五张图为非门内部sch

电源VDD上的波动通过非门到SW选通信号,进而影响Iptat,最终影响VBG,极大的降低了PSRR,请问各位前辈是否有好的建议

你需要把你的开关show出来,另外和电阻的链接关系用草图画出。 trimming的电阻选择不合适。

如图所示

这样电路容易清楚,你用开关内阻来短接一个小step电阻,那么需要开关电阻要比step电阻小的多。

你的设计问题:

1. 由于 短接电阻的点位约0.7V左右,所以无需 cmos TG,仅仅nmos即可,该处pmos 始终是cut-off的。

2. 减少开关的数目, 开关短接的电阻数目可以1/2/4/8. 无需额外译码。这样开关减少到1/4.

其实这不是问题,关键你triming的电阻很敏感,且阻值小,对设计的性能影响很大,不建议triming该电租,改成其它电阻。

楼上的建议都很有道理

小编,你说的:电源VDD上的波动通过非门到SW选通信号,进而影响Iptat,最终影响VBG。

不大可能吧,SW选通信号接的是开关的栅极,怎么影响的Iptat。、

就算串扰过去影响,也只是很高的频率部分,怎么样也不会影响到100K以下的psrr

vdd上波动当然能通过sw直接耦合至bg输出了。trimming时无法避免。我们仿真的时候,都是把选定register相关电阻拉粗来,不要sw进行仿真的。但事实上,我觉得我们的做法都不是真实应用环境,所以看到的pssr其实并不代表真实情况。但又没有好的解决方法。除非不用register,直接用otp烧不同值测试,最终选择合适电压,烧死,避免通过sw耦合。

哦,otp也是sw,也不行。还是等大神吧。

非常感谢您的建议,我会认真考虑

应该是通过影响SW的电阻值从而影响Iptat,进而传递到VBG

还是非常感谢您的回复

我就纳了闷了。按道理最多只可能是高频串扰过去,低频的psrr不会受影响啊。

我特意搭了个跟bandgap电路,进行了仿真,没发现开关对psrr有影响。