悬空的Nwell会引起Latch-up或其他问题吗?

时间:10-02

整理:3721RD

点击:

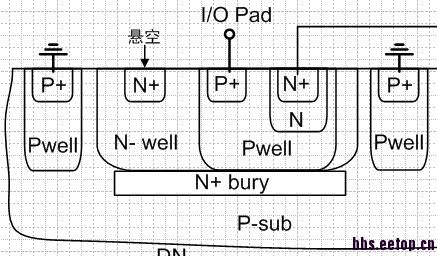

Diode做在Nwell中,但Nwell悬空,会引起什么问题吗(比如latchup)?

总感觉一个掺杂层悬空可能会引起某些问题

同问,见过一些版图POLY电阻下面nwell悬空,不知道是否有可靠性的问题

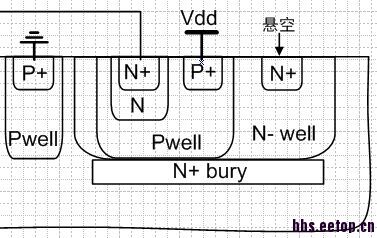

悬空在 CMOS工艺里都不好的吧,一般CMOS器件的栅极不能悬空,是因为 一旦 FLOATING, 由于是有源器件,一旦上电后,泄露电荷会累积到一定程度而产生一定的电压,此电压浮动不固定。还有,如果外界有静电,也会引起一些破坏等等。一般Nwell接最高点位,PWELL或PSUB接最低点位,这样可以有效的避免寄生PN导通。否则,一旦floating,结果就很难预料了,如果工作的时候,突然来了一个噪声,那NWELL上的电荷会不会一直累积,或者一直泄露。这样就很不安全了。

多谢多谢

见到过由于阱点位不定而导致的latch up现象,这个东西危险性很大

要是芯片上只有你上面的图的结构,是不会发生latch up的,因为没有n+接地,pnpn的结构没有放电的通路,但是整颗芯片不会没有n+接地的,而这个n+的psub没接好,就会有危险

借这个位置正好问下做在nwell里的Zener Diode的衬底是不是要接电源?

此处floating的N是为了增加ESD耐压,平缓表面电力线分布,防止表面击穿,高压经常使用这种处理方式。

HNWELL悬空在高压器件里面很常见的。不过NWELL悬空就不晓得了

多谢多谢,我仔细看了下,这里就是HVNwell

谢谢!

难道不是和nbl连的

学习,学习。

ESD的大神好多啊

好帖来支持支持