电压比较器DC输出上升慢

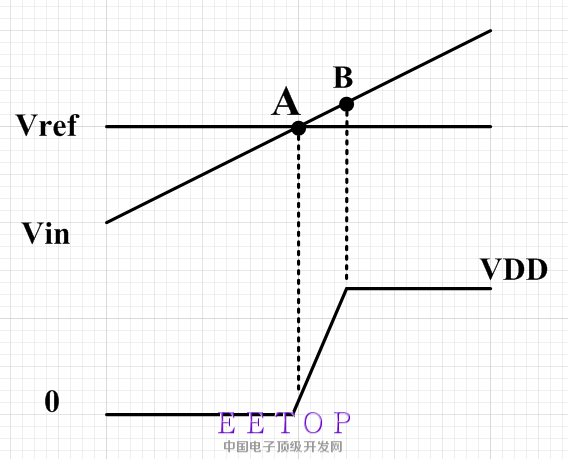

比较器结构为普通的二级运放,且输出有逐级放大的四级反相器.如图所示,上面为比较器输入曲线,测试时是DC输入,Vin step 1mV增加,下图为反相器输出的测试结果,A、B两点大约15mV。可以看出输出不是直接从0变化到VDD ,有个“缓慢”的上升过程,请问有人遇到过这种情况吗,或者说电路出现什么改变的时候,输出会出现这种情况?个人认为不是offset的影响,只是想不通经过四级反相器输出怎么会出现这种情况。

有人有想法吗

问一个问题,你上图是整个统计结果,还是单个结果?比如,当输入为固定电平vref+10mV时,输出始终达不到VDD吗?

单个结果,输出是稳定的,如果输入在AB中间,输出达不到VDD,给的输入是DC,所以不存在建立时间的问题

不知道

有可能是仿真器精度过低,尝试提高精度试试。

不是仿真,是测试时发现的

从图中只能知道比较器增益不够

是的,如果从结果倒推的话是由增益太小导致的,但是想着后面有四级逐级递增的反相器,又觉得不可能。

反向器很多情况下只是让0-vdd更加饱和,对于上升速度的并不是万能的。如果前级比较器增益不够,输出电压变化缓慢甚至输出摆幅很低。即使有inverter效果也不会好(要清楚mos的本质是voltage control current source才能对设计更加了解)。我觉得要想有小的over-drive(所谓的上升速度),还是要侧重于比较器本身而不是inverter这样的欺骗手法。你可以把两级放大器换成正儿八经的比较器设计,比如带正反馈的 或者使用latch结构。

你说的我部分认同,我是DC测试,输出虽然有点“慢”,但是最终还是会到VDD,所以比较器的DC输出范围可以达到0~VDD,对于后级反相器,当比较器输出的DC值在VDD/2附近时,反相器可当做放大器。根据测试结果15mV上升到VDD(2.5V),那么DC增益约为45dB,抛开比较器的DC增益,四级反相器的增益不至于不到45dB吧

inverter本身的增益不好说啊。比如我之前做的comparator,前级比较器增益50+dB,带上inverter以后的增益就测就是负的,这是很正常的现象,因为此时inverter的功能只是提供满幅和对后级数字电路的负载能力,所以工作区间的选择决定了它有没有增益。你可以回到仿真,把每一级都测一下,增益、摆幅、over deive,然后一步一步的找问题

哎,谁说不是呢 现在电路我各种情况都仿了就是复现不了这个现象,我人为的降低比较器的增益也没用。

其实你这15mV的over drive已经算是挺小的了吧。

算差的吧, DC都这样,瞬态性能不就更差了