pss仿真求jitter

怎么通过相位噪声来求jitter?

cadence那个里面有一个积分区间,我主要是想知道这个区间怎么选择?

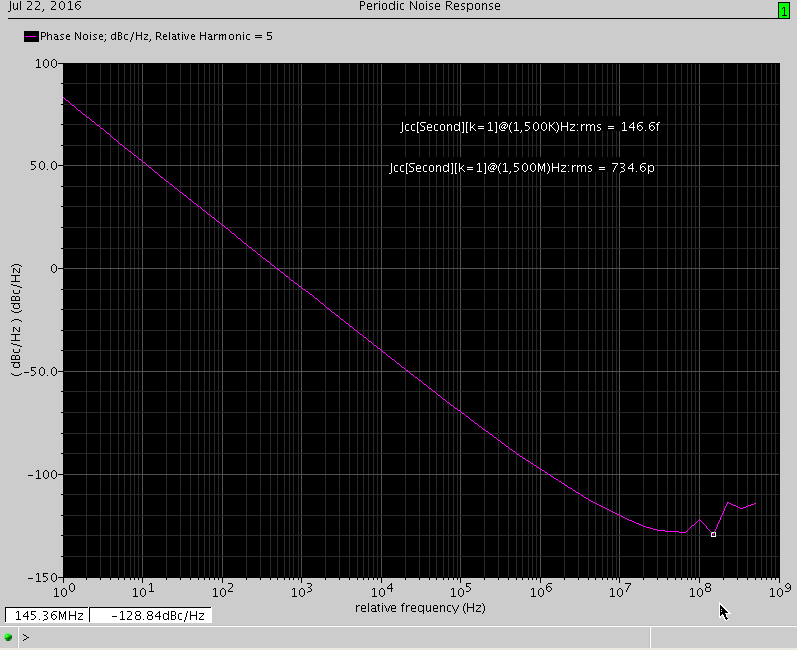

比如选择1~500K,结果是150fs,

如果选择1~500M,结果是730ps。

差距很大,这个区间怎么选择?

顺便问下,我仿真出来的相位噪声感觉有问题,怎么会有dBc大约0的情况啊,看下图

顶

pnoise里最下边有个选项,默认是source,改成jitter就可以了

10Hz到fosc或者fosc/2

对于这个来说,就是10-55M就可以了?首先谢谢回答

再就是想问下,那后面的为什么不用考虑了?我发现如果加入后面的频率,结果变化还是很大的。

一个55M频率的时钟,积分区间:1-25M是19ps

1-50M是25ps

1-100M是45ps

对于这个频率来说,积分区间对于最后结果影响还是很大的。具体该如何选择?

谢谢

dBc是指噪声相对载波的大小吧,在低频率下1/f噪声为主要噪声来源,积分出来的噪声如果比载波的功率还大,那就有可能大于0吧,可以在noise summary里看一下噪声的分布情况及大小。

可能是要看系统工程师的需求

不同应用要求不一样

能否具体说一下,或者相关的文档。我这边震荡出一个55M的时钟,我如果只是单纯看这个时钟的抖动,怎么计算。

一般时钟都有个jitter,他们的jitter是按照什么标准来做的。

简单说就是我就想看,一个上升沿到另一个上升沿的jitter是多少。

谢谢

能否具体说一下啊有个文档说明更好啊,谢谢啊

我现在想确认时钟从一个上升沿到另一个上升沿的jitter是多少。

我也碰到这个问题了,应该是看jee吧

看看效果

积分带宽的选择和应用有很大关系的啊。 你这个我不是很了解,但是对于一般的通信系统来说,积分带宽和数据包的长度以及信号带宽有关。 你的振荡在55M, 上限最大只能选在55/2。 总之jitter是噪声总能量在时域的表现,噪声总能量和相位噪声的曲线以及积分带宽有关。 对一般的驱动电路来说,低频是1/f噪声,所以积分的下限影响不大,你就比较好选。但是你的是振荡器,低频是1/f^3,积分的下限影响也会比较大。

谢谢答复,有没有相关资料可以介绍下

资料倒是没有,不过你可以自己写个matlab自己试试不同的积分带宽对不同类型的噪声的影响。关于相位噪声和jitter的关系,网上随便百度一下应该就有很多。