关于class AB运放稳定性的一个问题

时间:10-02

整理:3721RD

点击:

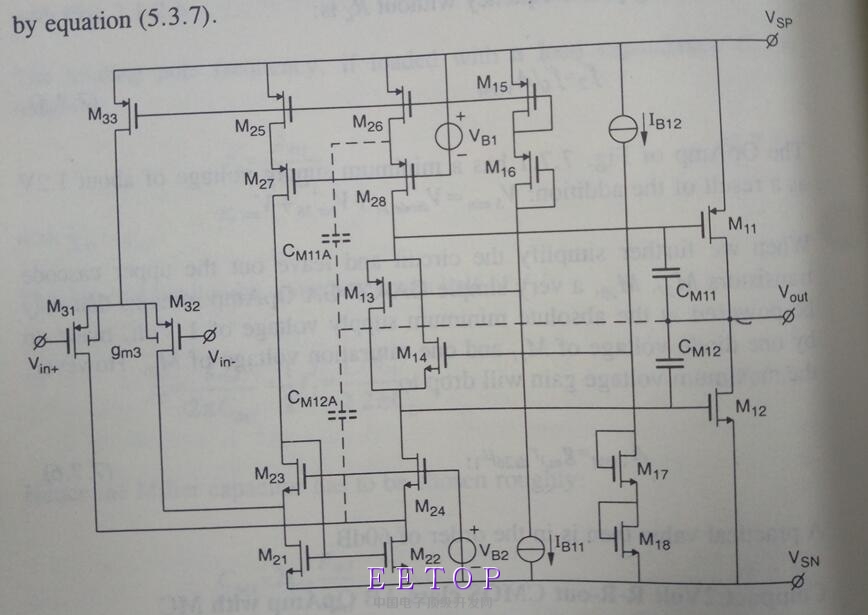

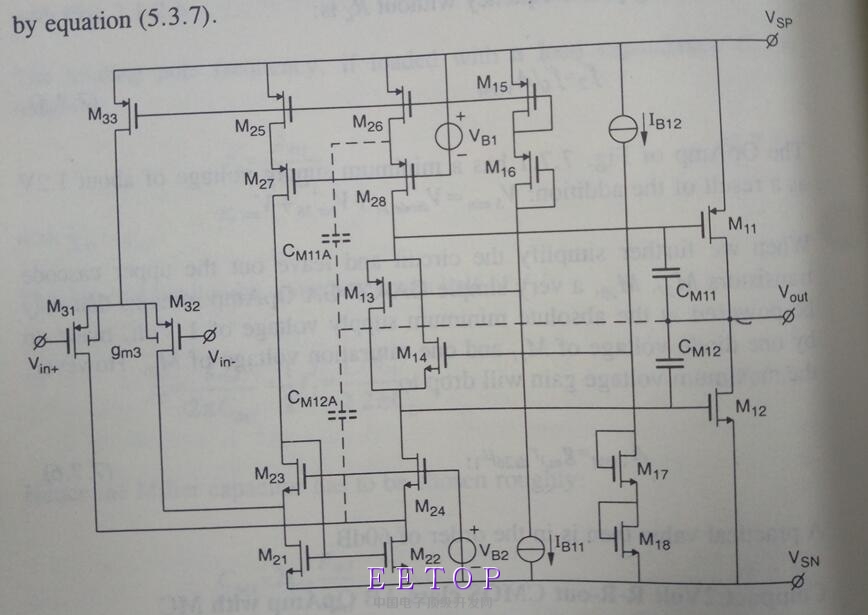

最近使用一个比较经典的CLASS AB结构,大致如图所示:

现在把它结成unity gain buffer,在反馈上插入iprobe看稳定性。用的5V器件,发现M13和M14的VDS电压超过2点几V,整个loop phase就会从0开始,loop gain也会偏离正常值。此时检查DC点都正常,瞬态step response也正常,反馈极性不可能接错。不知道是不是M13和M14这个小环路在影响loop gain 仿真结果?有人遇到过吗

现在把它结成unity gain buffer,在反馈上插入iprobe看稳定性。用的5V器件,发现M13和M14的VDS电压超过2点几V,整个loop phase就会从0开始,loop gain也会偏离正常值。此时检查DC点都正常,瞬态step response也正常,反馈极性不可能接错。不知道是不是M13和M14这个小环路在影响loop gain 仿真结果?有人遇到过吗

当M13,M14的Vds较高时,衬底漏电比较大,会造成相位曲线从0度开始,把M13,M14的S,B短接后一般没有这个问题。不过这个问题好像不会影响运放的正常使用。

http://bbs.eetop.cn/thread-290155-1-1.html

请看27#的解答

感谢回答,我困扰了两天了。那么我真的需要把SB接在一起去流片吗?如果说选择忽略这个问题,那么我仿真得到的带宽,相位裕度,开环增益都是不可信的,我又怎么来验证我的设计呢

这个现象对loop gain影响不大,但你说偏离正常值就有问题了,不知道你仿真的这个case是在什么条件下

小编,你的截图是哪本书上?谢谢!

每个环路都需要稳定

J. Huijsing的运算放大器

谢谢!

如果用在低功耗,管子工作在亚阈值区,M13和M14的离子化效应会对稳定性有影响,解决一个是SB端接,或者加大偏置电流,当然,和你的VBIAS电压有关系,自己取一个折中,离子化效应在格里那本书有