开关,电容,buffer,带宽,过冲,

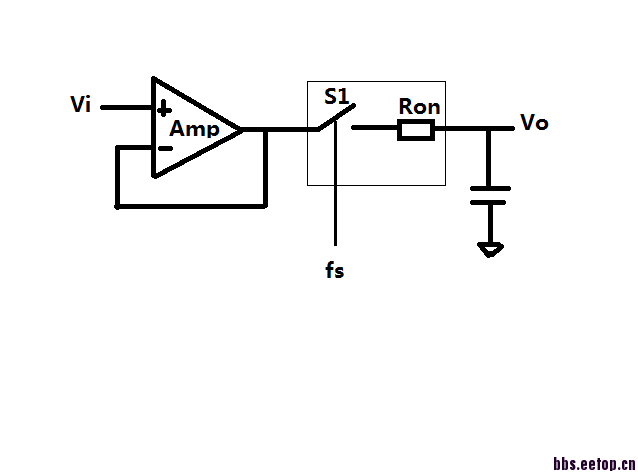

如上图,单位增益的buffer,开关s1断开时,

在输入端加一个阶跃信号,输出Vo跟随阶跃变化,而且没有过冲和振铃。buffer稳定输出Vo=Vi。

当输出Vo稳定后,开关闭合,buffer的输出Vo会有过冲和振铃。

这个过冲和振铃和开关的导通电阻有关。导通电阻很小时过冲很大,导通电阻很大时,过冲就没有了,但是建立时间需要很久(和Ron和C的时间常数相关)。

请问怎么解释?

运放的带宽和相位裕度都是足够的。

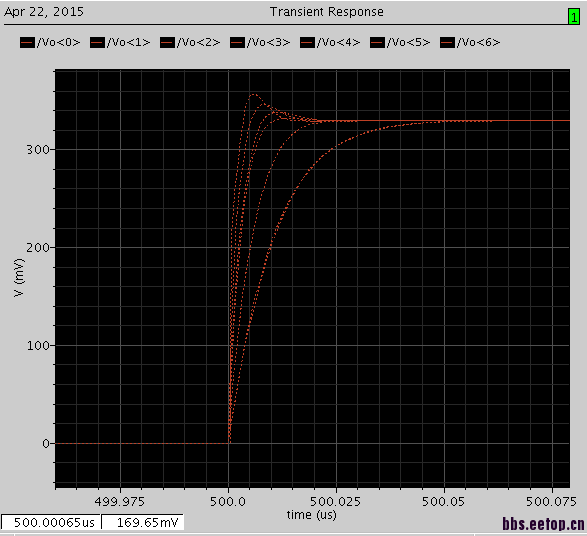

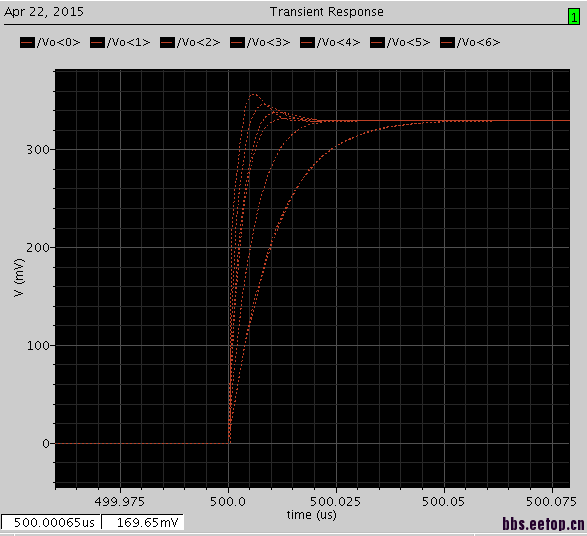

下图是仿真结果,改变开关的导通电阻,过冲和振铃情况就改变

Vo是差分值,初始时电容上都被充上了VCM的共模电平,所以输出是0,开关闭合后,电容上最终的差分电压就是输入电压Vi=330mV

在buffer的输出端加开关的闭、合,和直接在输入端加阶跃信号,输出Vo的响应还不一样。

请大神指点

这么好的问题,不能沉底啊。顶

直观理解,电阻对电荷有阻挡作用,开关断开过程中,输出为电容上积累的电荷,因没有电荷补给,自然没有过冲;当开关闭合时,buffer对电容存在充放电荷作用,就那充电过程来讲,若电阻越小,对电荷阻挡作用越弱,瞬间电流越大,表现的就是电容上极板电压存在过冲,类似于boost原理。

PS:推测电路是为负载提供电流的,相当于一个pump电路或者boost电路,电阻前边加一个缓冲电容可以改善电路特性哦。

谢谢回复。

不过我认为知道现象后很容易先入为主。

如果我得到了相反的结果,减小开关的导通电阻,过冲也减小,肯定会有人给出相应的解释的。

能否从定量分析的角度,退出这个电阻和负载电容(或者和运放带宽,摆率....)与过冲的关系?

电阻大于什么值的时候,过冲会消失?

汗,我们思考问题的方法和角度不一样。增大开关的导通电阻,过冲一般是减小的,但效果非常不明显吧,还不如加大输出电容呢。如果硬是从运放考虑的话,那你SR小一点,相当于减小了对后边电容的充电速度,也是可以的;同时减小带宽,相当于衰减乃至滤去了高频成分,由于在开关闭合的瞬间,电阻表现为感性,因此也可以减小一些过冲吧,但效果没有减小SR来得明显。还有,导通瞬间,如果对外提供电流,那么开关电阻+后边接地电阻,必然会影响输出零极点,增大带宽,如前所述,这本身也会造成一些过冲。

那具体是不是这样子,你可以跑下仿真验证一下。期待你的结果。

还有,如果你减小开关电阻,真的过冲减小了,你不妨尝试单独减小后边电阻,是不是会得到相同的结果。如果减小后边电阻,反而变差或者没有效果的话,那由于电荷传输主支路上就一条通路,就只能是开关管的馈通作用了。

我图中的电阻是等效的开关的导通电阻。

从我仿真的结果来看,增大开关的导通电阻可以显著减小过冲。

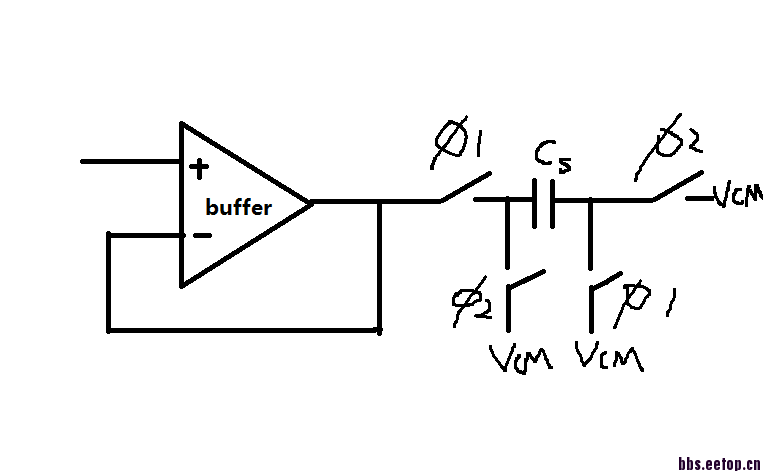

你可以仿仿看:(常见的开关电容电路)

如果用理想的开关,过冲是最大的。

增大开关的导通电阻,1kΩ,2kΩ,3kΩ......可以看到输出(Cs左极板)的过冲显著减小。

但是当电阻增大到RonCs这个时间常数很大时,建立时间就长了。

谢谢~

不过不是很明白这句话:“单独减小后面的电阻” ?

电阻都是开关的导通电阻。

其实我的意思和你的一样,就是在开关和buffer之间加一个电阻可以减小过冲。和开关的导通电阻是没关系。

不过我设计时希望不加电阻,而是通过开关的导通电阻来实现这个buffer和开关间的电阻。

总之,就是说在电容Cs前,开关导通时的电阻越大,过冲越小。

汗,我说的就是你加的电阻。原来你本来没有啊。

在运放输出加个小电容也行吧。

运放是什么结构?开环性能多少

buffer是一个实际电路,不是理想buffer,开关断开时,整个电路为网络A,开关闭合时,整个电路为网络B,网络A和网络B都是闭环电路,网络A有闭环极点P_a1,P_a2, .... 及对应的Q值Q_a1,Q_a2,....,网络B有闭环极点P_b1,P_b2, .... 及对应的Q值Q_b1,Q_b2,....,就是说,网络A和网络B有不同的Q值(或者说不同的阻尼系数ζ),相同的阶跃输入,输出自然不同,如果Q值>0.5(或者说ζ<1,或者说有复数根),则表现出过冲或振铃,如果Q值<0.5,你看到的就是平滑曲线

电阻值从小到大,则Q从大到小,曲线从过冲到平滑。

如果不希望过冲,应减少闭环buffer的Q值,即增大开环的相位裕度和增益裕度。

有一点应注意,不可将buffer等效为戴维南或诺顿

那输出端开关作用下的建立时间和输入加阶跃信号的建立时间是同一个吗?它们之间有什么关系?

不能用戴维南或诺顿等效,那应该怎么分析?传输函数?

楼上分析的不错、、、、

我对你这个问题挺感兴趣的,但是存在一些疑问。

1,你说的震荡是如何的震荡,是buffer的输入是变化值吗?,还是buffer的输入是一个恒定的值,而只是开关的动作引起了放大器的震荡。

2.理论上讲,开关的导通电阻会在传输函数上引起一个负的零点,它在一定程度上会增加系统的稳定性,从你说的结果看,应该是你放大器本身存在问题吧,不知道你的放大器在单独做瞬态仿真的时候会不会引起震荡的问题(ac仿真得到的相位裕度不是放大器不震荡的充分条件)。

最近做过这么个电路,BUF输出稳定后给AD的采样电路采样用,不过我主要关注cap的建立时间和精度。不知道小编有分析开关打开时候的瞬态电流、运放内部工作过程和顺序、开关打开前后的相位和带宽?和运放的压摆率、相位和带宽关系都挺大。

直观上,电阻越小,过冲会越大;电阻越大,建立时间会越长。

开关打开瞬间有一个大信号建立过程,然后是小信号带宽稳定过程,具体分析又说不准确……

It is possible to explain why the unloaded buffer is stable. But let's put it aside as another story.

If the buffer is abruptlyloaded with a R-C network, the case is different. First is slewing transition, during this phase the buffer works very hard in order to recover the output, which is rising edge in your figure.

After this phase, the buffer goes into class-A (or linear ) region, in this period if you look back into buffer's output, it will exhibit inductive impedance other than resistive. Then the whole circuit is simplified by voltage source, inductive output impedance and r-c network, if r is too small, then L-C oscillation will appear.

Looking back to slew rate tuning, if SR is chosen to be slow, then the buffer requires more time to return class-a opeation.If such aspan crosses the inductive-impedance region, then a smaller ringing can be observed. But it never disappears.

Such an issue it common in SAR ADC buffer design. You can refer to one TI's application note for more detail (title: I don't remember. Sorry,,,).

Good luck!

不一样,因为你的buffer是实际电路,显然不一样,至于它们什么关系,就是buffer越接近理想,2个波形越接近。

为什么不能等效戴维南,因为buffer是实际电路,闭环下是高阶电路,闭环极点2个以上,怎么能等效戴维南?

分析思路和方法就是,要把buffer,开关,及电容作为一个整体电路网络,而不是把buffer割裂成一个理想单元。我前面说整体电路网络A,网络B的Q值概念你应先理解,开环有足够相位裕度和增益裕度,则闭环Q值就不会高,即不会有过冲或振铃

遇到了和LZ类似的问题,同求解答

很厉害,学习了

可以理解为两个RC网络串联,第一个是你运放的输出电阻和电容,第二个是你开关管导通电阻和负载电容。当导通电阻较小时,两个级点很近,会产生过冲;当导通电阻变大, 第二个级点成为主级点,就变为一阶RC,观察到的就是时间常数。

你可以改下你运放的输出电阻,观察下输出波形变化来验证

楼上说的对,输出电阻变化会明显影响过冲现象,还是阻抗匹配问题,单独仿真不仅相位裕度 增益裕度也很重要!