浙江大学60GHz锁相环

最近听说浙江大学基于国内40nm CMOS工艺做出了60 GHz锁相环,测试性能也很好,国内工艺模型不是只支持到20 GHz吗?请问大家知道这是怎么实现的?

国内工艺厂的模型是都是只保证20GHz以下是准确的,而且没有互连线的模型,所以毫米波的锁相环很难设计。很多人都是用Tsmc或者Global的工艺做的,它们的模型很全。

浙大说他们是改了SPICE仿真的Model,但是不知道浙大是怎么改的。

这个是浙大微电所的60 GHz PLL的新闻报道。

http://www.isee.zju.edu.cn/ic/re ... d=14&object_id=4139

国外不是很早就出来了吗

谢谢你的回答。改模型前相噪频偏1M处只能到-70多db,修改模型模型后能到-90多db,浙大微电子确实牛!

还是回复一下的好,这个东西并没有那么神奇。哈哈。国内的工艺很多都是从国外买的知识产权,买的时候做了很多限制,比如只能使用在10GHz以下,其实模型是支持更高的频率。ZJU之所以没有说是哪一家流片,原因就在于此。只能说这么多了。

我们浙大用国内厂家提供的模型做60GHz PLL,2014年得到的第一次流片结果如第一张所示,相噪只有-73dBc/Hz@10M,

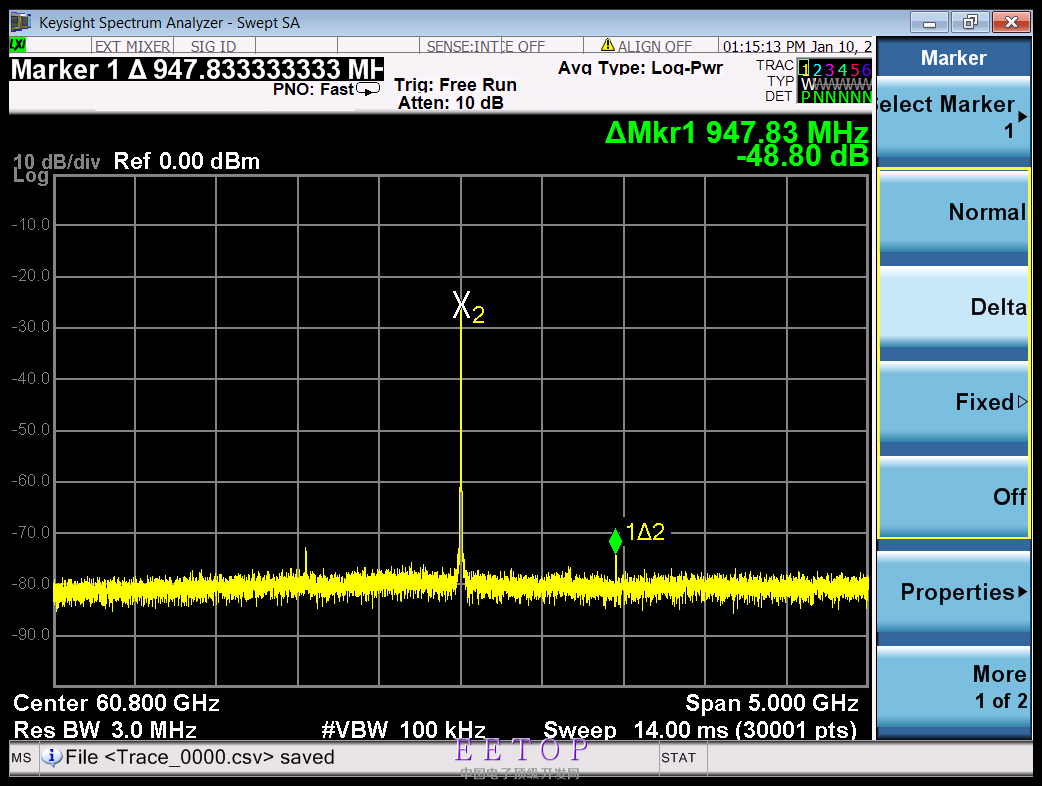

根据这张图,我们找到了原因并修改了模型,在2015年第二次流片时,即得到了如第二张图所示的较为理想的结果,相噪-110dBc/Hz@10M,-92dBc/Hz@1M

我们的流片厂购买半导体制造设备时和美国签订了出口限制条款,高性能PLL在不能制作条例之内。所以不能说。

40nm这玩艺也就smic的啦!都公开的秘密了,国内难道还有第三家在折腾40nm工艺?

另外有一个问题:实验室做出来的IC,测试结果是wafer level还是封测的结果?量产批还是MPW?

产业界最关心的是量产一致性,市场需要的是批量生产的产品而不是工艺品哦.

别人是科研!也就是发发论文而已

谢谢提醒! 呵呵

看到59GHz到61GHz我相信是发发文章玩的了60GHz应用时要7-9GHz带宽的

请问大神,MPW和量产批次会有什么不同吗?为什么每次说科研界和工业界是有区别的,毕竟浙大的也是WAFER测出来了,难道意思是只有一片测出这个性能,剩下的DIE的性能就变得很差吗?

请指教

请教一下,MPW和量产批有什么区别那,看了上面的图片是有一颗DIE测试的性能还不过,难道其他的DIE测试出来就会偏很多,有时不太明白有些人说的科研界和工业界的区别?

量产批会做Corner Split,各种Corner你都会遇到.而MPW就那么一点面积,某一个Corner下的值.

从设计角度看,电路留出的Margin是否足够,需要Mass Production后的测试参数才会发现.长期做MP的RD就会知道哪些参数需要修调,Margin预留多少比较合适.

另外,yield loss也会在生产wafer的各个环节发生,没有MP后在大批量测试上的考验,很难发现良率丢哪里了.

再次,Package环节,比如导电胶溢出,划片不当产生wafer破碎等等可以引起yield loss的因素.从版图角度看,也是可以解决部分问题的.

所以我说的做工艺品和做产品是本质的不同!

谢谢

做毫米波的人要有能力自己建模型啦。频率高了,很多东西都不准确了。

感谢耐心的解答!

还是要鼓励支持吧,毕竟能做出来,在国内的大环境下也是不易,很多东西要慢慢来,急不得的~

我也是乐了,和搞科研的谈良率这不是鸡同鸭讲么。

重新提模型。杭电cad所有套建模设备。照片上就是杭电的微波暗室。之所以是浙大的成果,是因为杭电的博士全是在浙大招的。

真心说,Foundry的工艺控制的还是比较一致的,MPW结果和量产差别也没那么大。做好工艺偏了能调整的预案即可。

1、“我也是乐了,和搞科研的谈良率这不是鸡同鸭讲么。”我想,您一棒子打了一大片辛苦做科研的人吧。难道做产品不都是从基础研究做起来的吗?您这样的说法不觉得不妥吗?

2、“杭电招的博士全在浙大招的”,这情况属实。但是,这不代表浙大就没有研究所教师研究生在做射频集成电路的吧。所以,你说的“之所以是浙大的成果,是因为杭电的博士全是在浙大招的”是否有不妥?

3、我们浙大这次做的锁相环芯片,是在杭电的CAD实验室测试的,他们的射频设备非常先进,杭电实验室在测试方面也给了我们很大的帮助,我们也很感激他们的帮忙。照片上的确实是杭电的测试环境,您的观察很细致;但是除了芯片测试,其他包括修改模型,芯片设计等等全部都由浙大微电子独立完成的,谢谢!

1、张研,不是我打击你,这就是国内的现状。高校的研究基本上产业化不了。希望你能正视这一点。我记得去年浙江省抽查产业创新项目,企业的6个基本都合格,而高校的6个都不合格。这是由于高校研究和产业界的根本目的不同,高校研究追求的是“新、奇、特”,容易发paper,报专利,写基金,申项目。没有企业追求的“降低成本,提高利润”的原动力,所以谓之“鸡同鸭讲”。

2、我解释的是为什么实验是在杭电做的,却不是杭电的成果,也没有体现杭电参与这项工作。这是因为在杭电参与这项工作的博士研究生,都是杭电从浙大招的,实际都是浙大的人员在工作。并没有说这不是浙大所做的工作,你的理解有偏颇。

3、既然我能知道你们的实验地点是杭电的微波暗室,那么我自然也有能力了解你们工作的详细内容。所以你不用和我解释。

牛

我想知道,你说基于第一张图,你们找到原因,所以将相噪降低到-90dB@1M. 请问这里的故事是什么?能分享一下吗,谢谢。

这个要业内人爆料了

牛

学习了

我也想知道这个~

锁相环的新闻在官网上怎么没了

你们的锁相环新闻怎么没了