对ADC的输出做FFT

时间:10-02

整理:3721RD

点击:

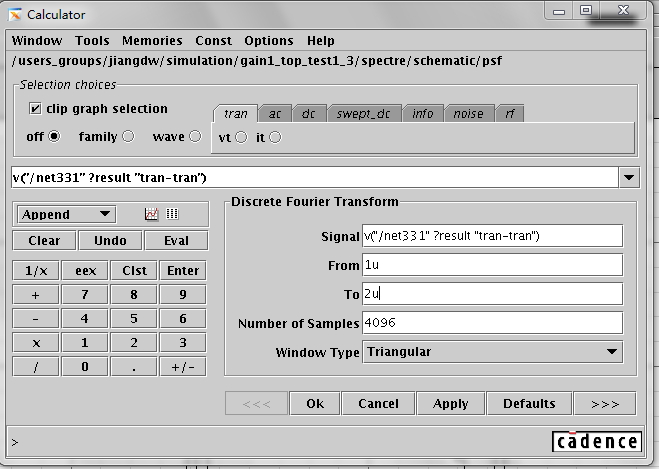

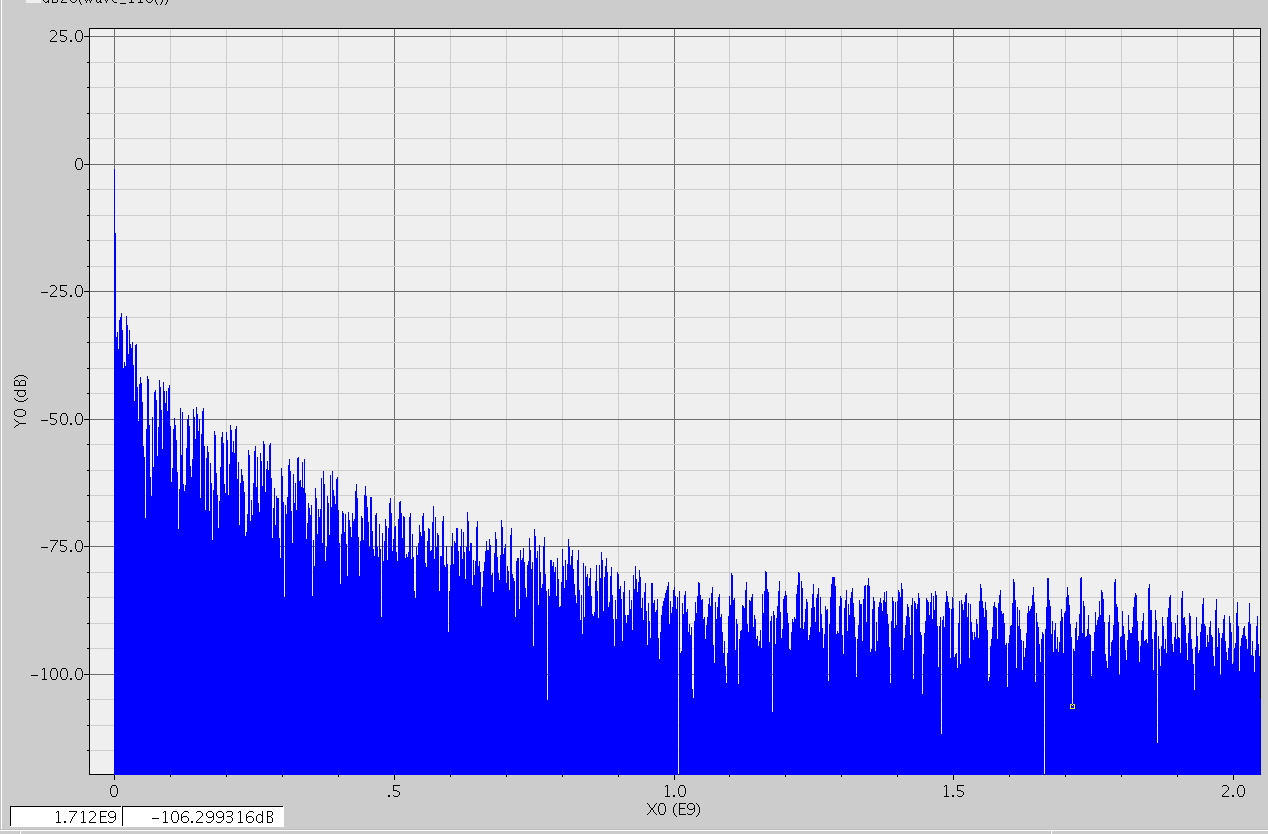

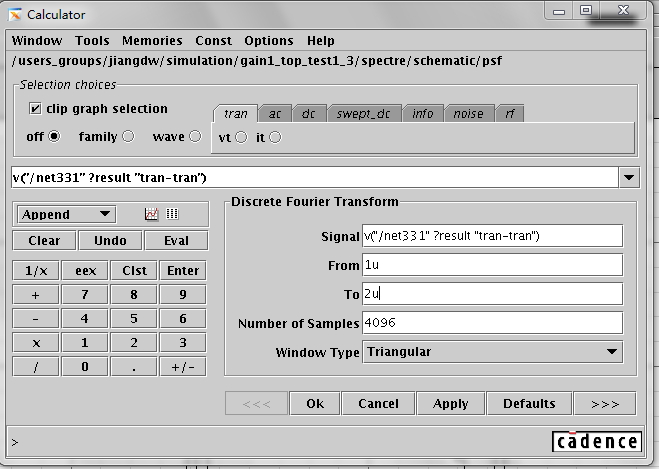

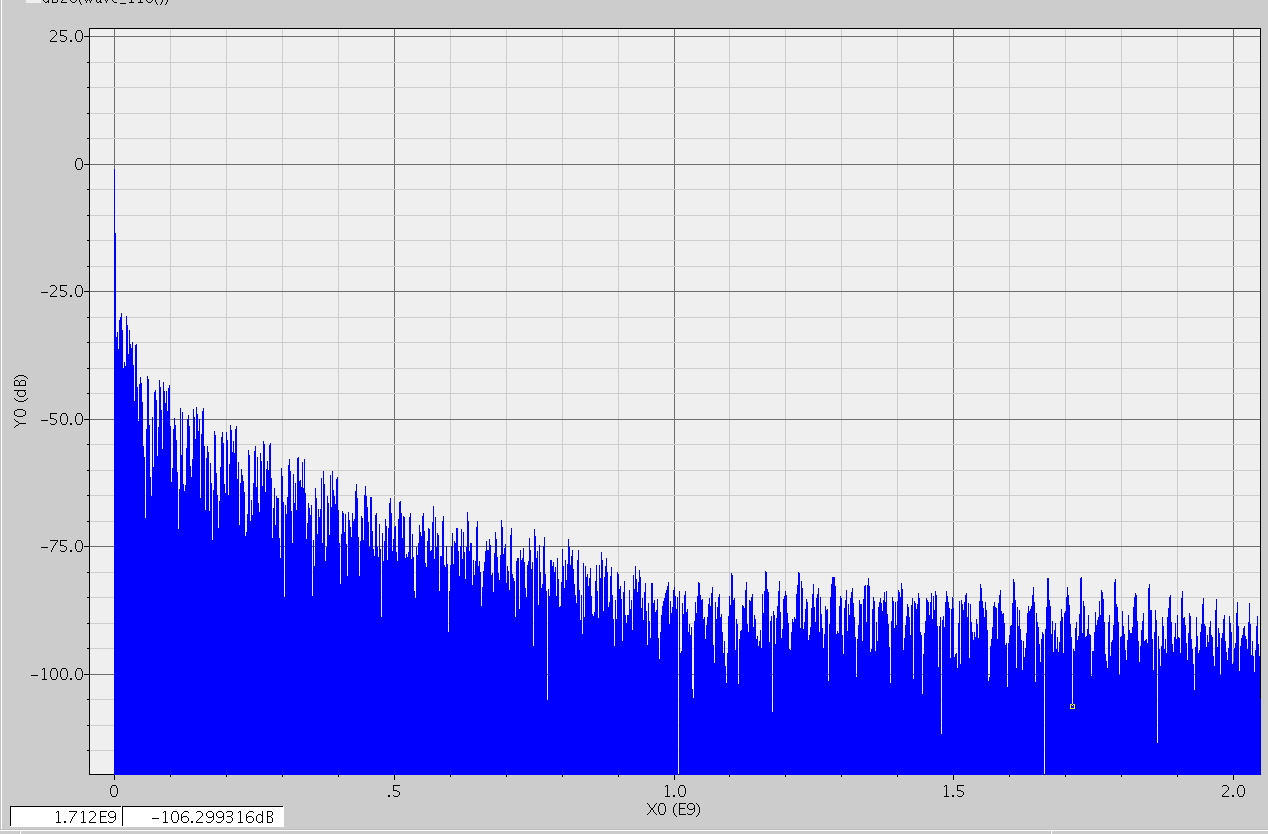

最近在做一个12bit的一个ADC,最终能够输出12bit的数字编码,但是不知道如何做FFT才能看到SfDR等性能指标,工具用的是cadence。我是首先利用一个理想的DAC,输出结果如图一,然后我对这个信号做了DFT,然后20lg转换为dB,得出图三的结果,这样看着不太对啊。我采样信号为60M,输入信号给的是60M*137/8192。

小编,感觉您那个理想的DAC的输出波形不太对。

你是说一个周期内有四个不在包络上的点吗

我看了一下理想DAC的程序,主要是加权求和然后/2^N,需不需要滤波器,我也不太懂,目前ADC就做到这,不知道怎么看参数

个人认为不是DAC的事情。建议您在输入加一个斜坡信号,看看输出的12位信号是不是从000000000000~111111111111变化。正确的信号应该是后面的12位比前面的12位大“1”,并且所有的12位信号只能出现1次。

你说的是不是理想的ADC,非理想的ADC能够输出所有编码吗,有效位就8--10的样子

还有人给指点一下吗

如果是仿真的话,应该接近12位,比如11.98位等。但加上斜坡信号,肯定会有12位输出码,而且前后码相差1。

您说的8-10位,应该是流片后的测试结果。如果仿真只有8-10位的话,那设计肯定是有问题的。

这个输出不对啊,应该是单调的吧~

calc里有个sample函数,可以先对这输出波形采样再做DFT就比较正了~

cal原来这么强大

1u到2u之间取不到4096个点,时间应该是(1/fs)*采样点数,4096个点时间太长了

标题

小编在吗

确实不对,基本概念好像都不对