Sigma-Delta ADC SNR仿真时频谱中出现了输入信号的各阶谐波,求解答

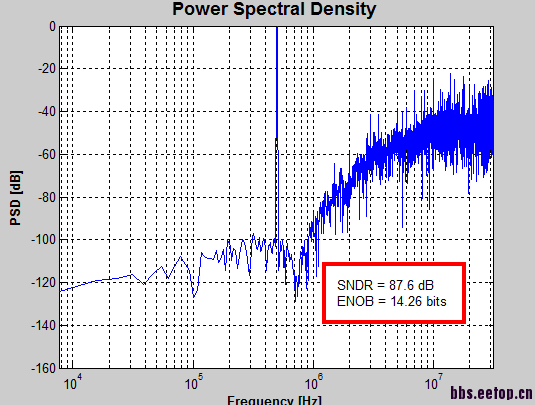

上图为matlab系统建模后的理想频谱。可以达到87.6dB。

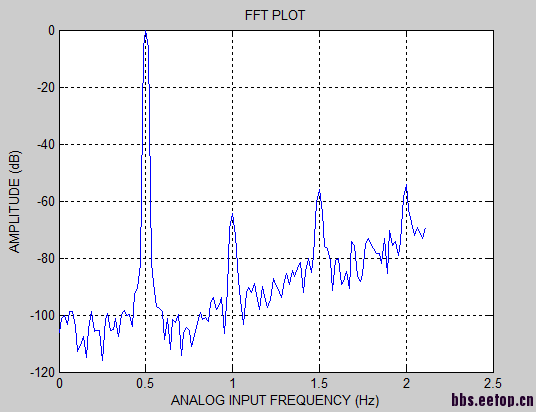

这张图是实际的电路仿真的频谱。可以看到在DC,1M,1.5M处出现可谐波。SNR只有71点几dB。

请问如何会出现这样的现象?

我记得1次谐波是非线性引起的,2次谐波是非对称引起的,1.5次呢?

DAC开关时候把信号卷进来的,DEM没做吧?

没看到DC的谐波啊

我的输入信号中心频率是500K的,没有出现1.5次的啊。

信噪比60多一些,实际电路做的与理想差的多一些啊

我现在仿真的时候DAC用的是理想的电流源。我反馈回路中用了三个DAC,当然反馈电流不一样。电路工作的时候反馈电流是一直存在的。您说的DAC开关是指的什么时候开关?还有就是我不太懂您说的DEM是什么意思?

我说的开关是实际电流镜的开关,DEM是校准电流镜失配的模块,既然你说是理想的,那么和这个没关系。可是你帖子说是实际电路阿。

你最好说明哪些是理想哪些是实际的?

现在仿真时用的除了电流源之外其他都是实际电路。包括放大器、比较器和DAC驱动电路。我也尝试着改变滤波器的参数寻找问题大根源,发现没有用,都会出现相同的情况。

是啊,就是遇到这个问题了。如果解决这个问题,估计会达到80dB左右吧。

其他不变,你把运放换成理想的仿一下,看看结果再说

我起初的想法是想用全理想的去仿真的,但是我一旦把放大器换成理想的,仿真就会报错,说mos管超过了最大电流被击穿,我就很无奈了

为什么一次谐波是非线性造成的,二次谐波是由失配造成的呢?

报错?这种应该是warning啊,理想运放就用vcvs就行了啊,规定好max/min output

看错了,只有奇次和偶次的。

你看下拉扎维非线性与失真那章。

减小输入或(和)参考电压试试

小弟也在学习做一个sigma-delta ADC想问你一下在simulink中怎么测试ADC的SNR啊?刚开始接触,很多不懂,见谅,求指导一下

兄弟,做的怎样了?交流一下~

请问小编,matlab行为建模时的半周期延时是怎么做的啊?非常感谢!

我发现你的输入信号用的是0dBFS,这样很容易造成overload,可以将如入信号amplitude改成-3.5dBFS或者-6dBFS试试

最后发现确实是积分器的非线性引起的,引入了谐波。谢谢。

DEM做了,采用的是DWA算法呢。

感谢您的回复,问题已经解决,最终发现时积分器非线性引入谐波,谢谢。

不客气啊,以后我研究sigma delta时候请教你啊。

请教谈不上,大家相互交流。

我的输入电压是FS的0.8倍,这么大的输入应该是安全的输入电压吧。还有就是,我想知道,你是怎么看出来我输入的是0dBFS的呢?

现在matlab仿真,吧里就有相应的函数文件的,你找一下应该能找到。

SDtoolbox里面没有半周期延时模块,只有单位周期延时模块。那就把单位周期模块的采样时间手动改为时钟周期的一半就可以了

向您求教个问题,现在我实际电路仿真出来了,我想计算它的THD,但不知道怎么计算?

我只知道在feedforward结构的经验值: 3rd-order的modulator用0.5或者0.67的VFS,而2nd-order用0.67或者0.75。

我看你的PSD上信号在0dB所以以为是你用的VFS的输入幅度,因为我一般画PSD时候都是refer到VFS的。