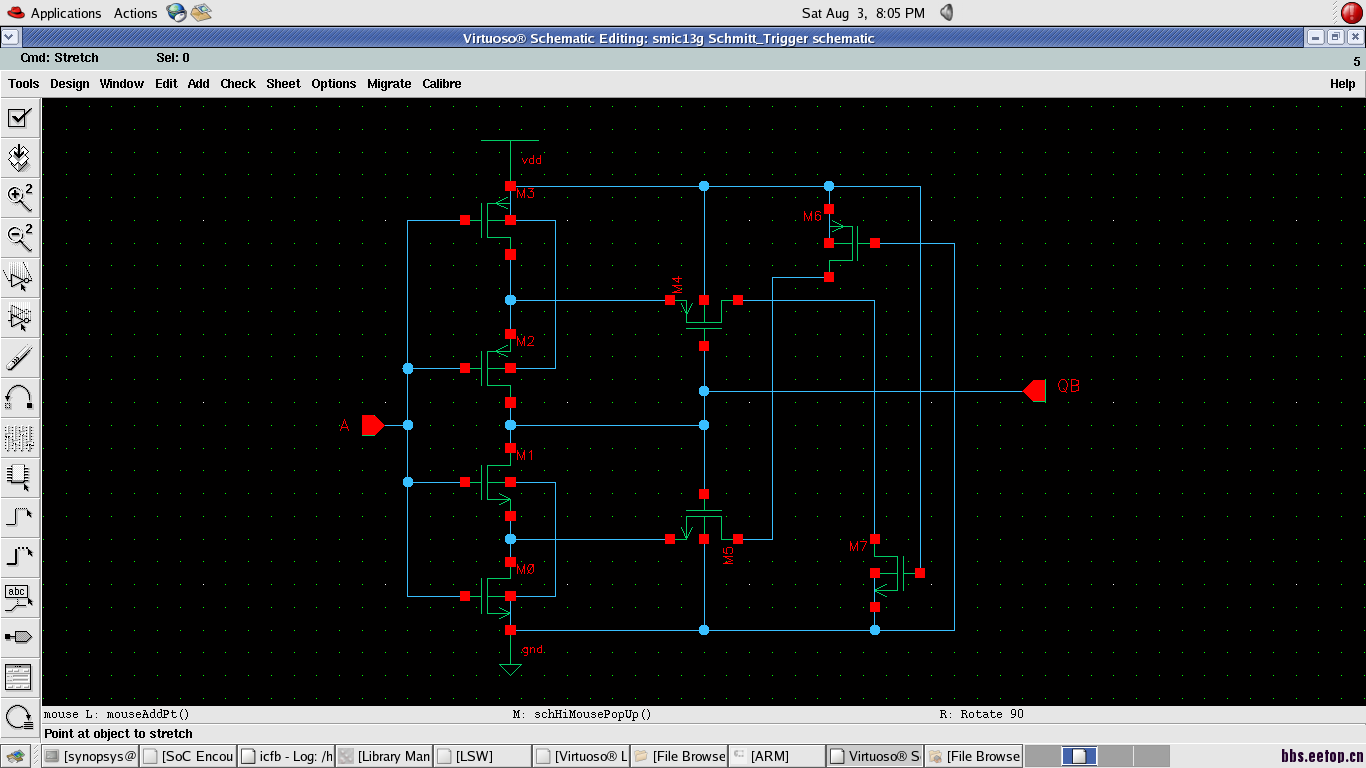

CMOS Schmitt Trigger电路防止Latch up的两个MOS的理解

时间:10-02

整理:3721RD

点击:

听同事说M6、M7的接法可以防止Latch up,哪位大侠帮解释一下M6、M7的接法可以防止Latch up的原理?

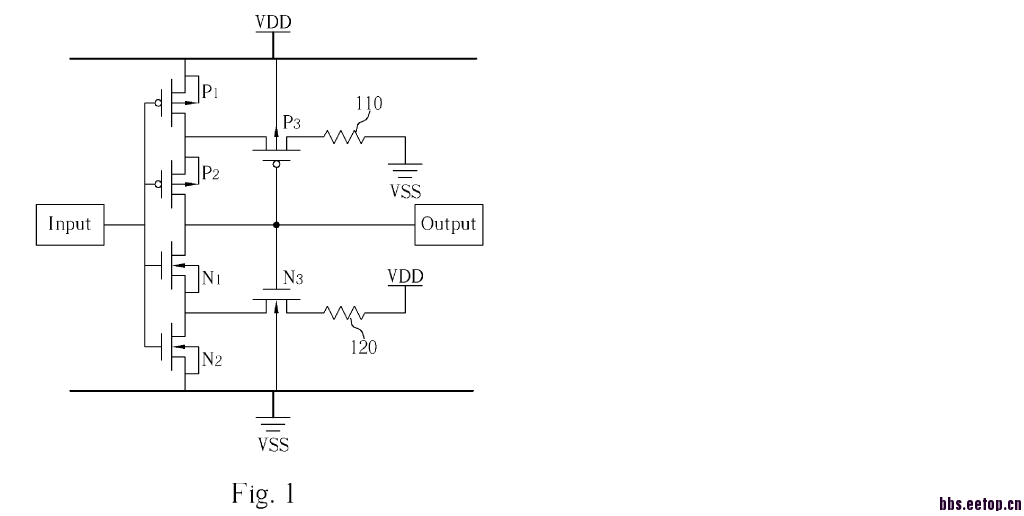

功用跟這篇專利的 Resistor 雷同。

http://www.google.com/patents/US20070052465

不错的文档,文中只是说接110 或者120欧姆的电阻,可以防止ESD,并没解释可以防止ESD的原理

继续等大侠们解惑

这个需要纵向剖面图来解释了

上图的P1、P3对VIN和VSS来说是低阻通路;同样的N2、N3对VIN和VSS来说也是低阻通路。比如说打VDD对VSS的ESD时,P1、P3或者N2、N3可能导通从而泄放ESD能量,这是不希望看到的。我刚工作那会,公司强调过这个,之前有芯片SCHMITT出了问题

learning !