TX CML设计

时间:10-02

整理:3721RD

点击:

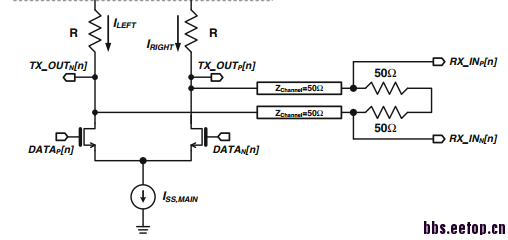

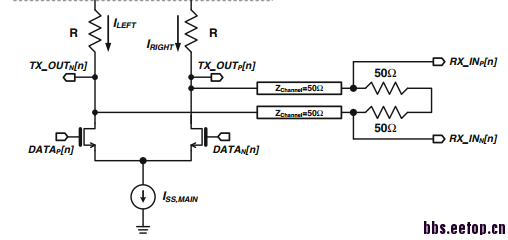

最近在做一个TX用的CML driver 电路,CML的输出便拉到PAD,过键合线,走背板,然后到对方接收器。背板走线据说可以模拟为两条50Ω的微带线。

所以,电路如下图所示:

本设计CML希望达到差分1600mV的输出,所以给的电流源是16mA的,上拉电阻是50Ω,以跟传输线匹配。

但不接后面的电路时,CML确实可以有差分1600mV的摆幅,但接上负载电路后,摆幅就下降到了差分600mV。

请问为了获得1600mV的摆幅是需要将电流源增大到16*2mA么?还是说我的电路模型不合理呢?

望做过SerDes CML电路的指点下~

所以,电路如下图所示:

本设计CML希望达到差分1600mV的输出,所以给的电流源是16mA的,上拉电阻是50Ω,以跟传输线匹配。

但不接后面的电路时,CML确实可以有差分1600mV的摆幅,但接上负载电路后,摆幅就下降到了差分600mV。

请问为了获得1600mV的摆幅是需要将电流源增大到16*2mA么?还是说我的电路模型不合理呢?

望做过SerDes CML电路的指点下~

TX输出的幅度和RX那边看到的不一样,应该是RX那边只有一半。所以这个指标是输出吧,不应该考虑RX 那边。

在匹配情况下,TX 端看到的是 50/2 = 25 欧 ,16mA 电流,差分电压只有 800mV

你好,请问有没有介绍CML接负载工作分析的文章可以分享下?谢谢!

Tx和Rx都有termination的情况下,负载阻抗是50/2 ohm,I*25=1.6V. 不知道您的速度多少,电流增加后,input管尺寸也会增加,self-loading会加大,带宽会减小。

要输出differential peak-peak 1600mV, 阻抗如图匹配当然需要32mA电流。

知道了,谢谢~

比较合理的方式还是TX端本身不带上拉电阻

对,应该是RX

如果在此图的基础上,发送和接收端中间通过变压器耦合,变压器1:1,变压器会将接收端的电阻耦合到发送端么?对于发送端来说,负载电阻看作50/2=25Ω?