CPPLL的simulink建模仿真遇见的几个问题

时间:10-02

整理:3721RD

点击:

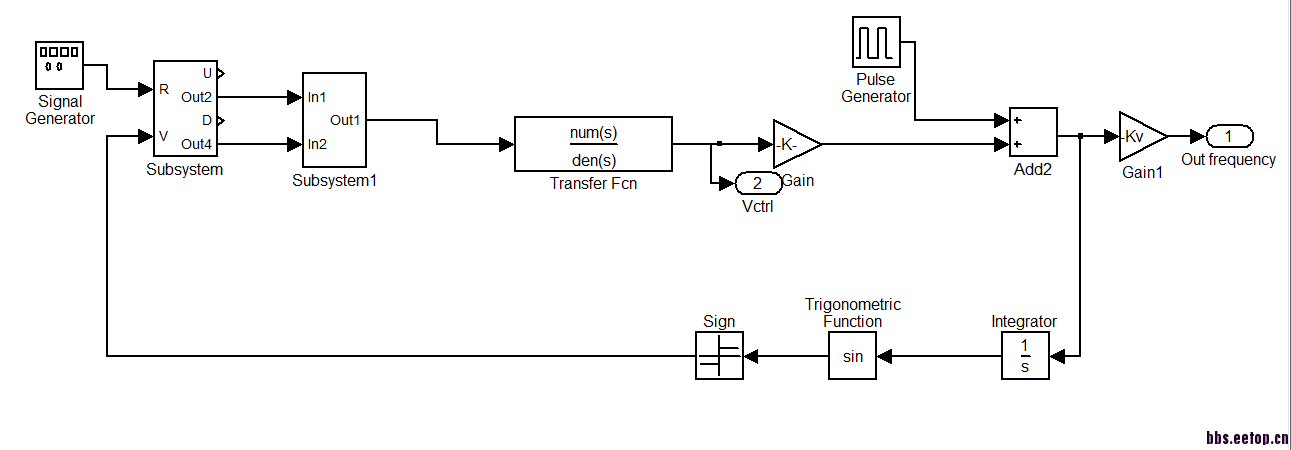

主要是自己放了一下得到的结果不太确定那里不好,想让做过的给指点一下首先结果大致应该是这个样子的吧

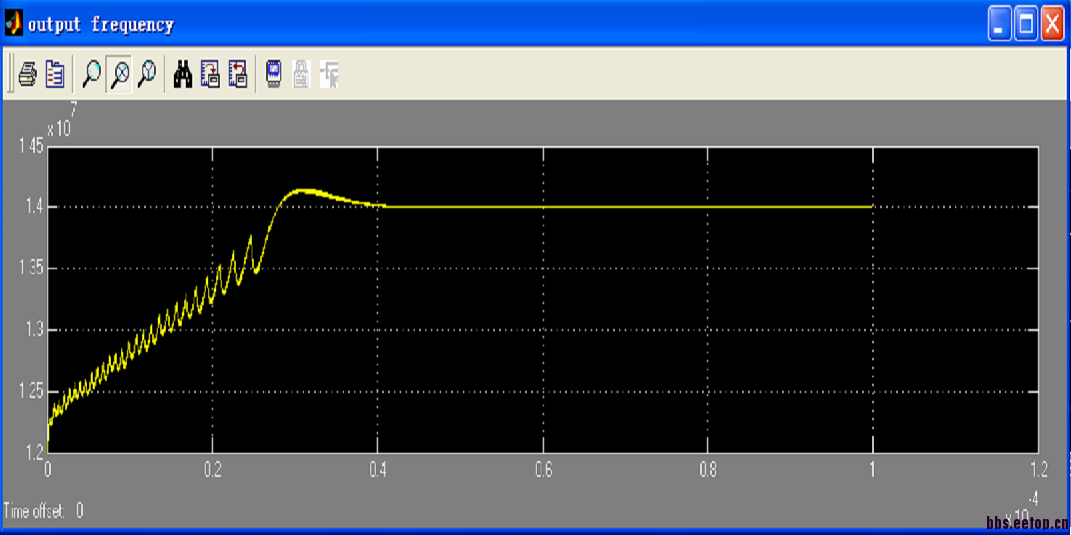

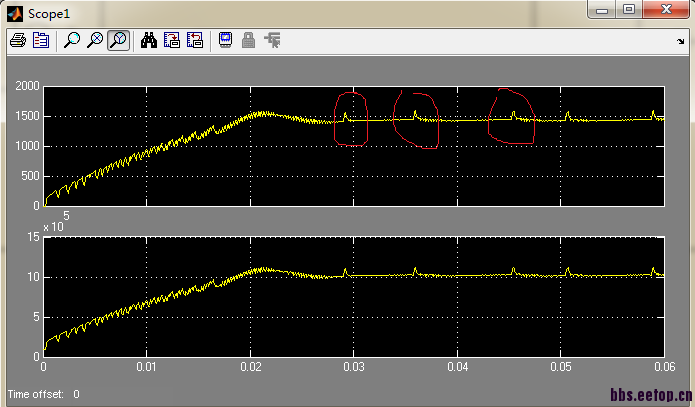

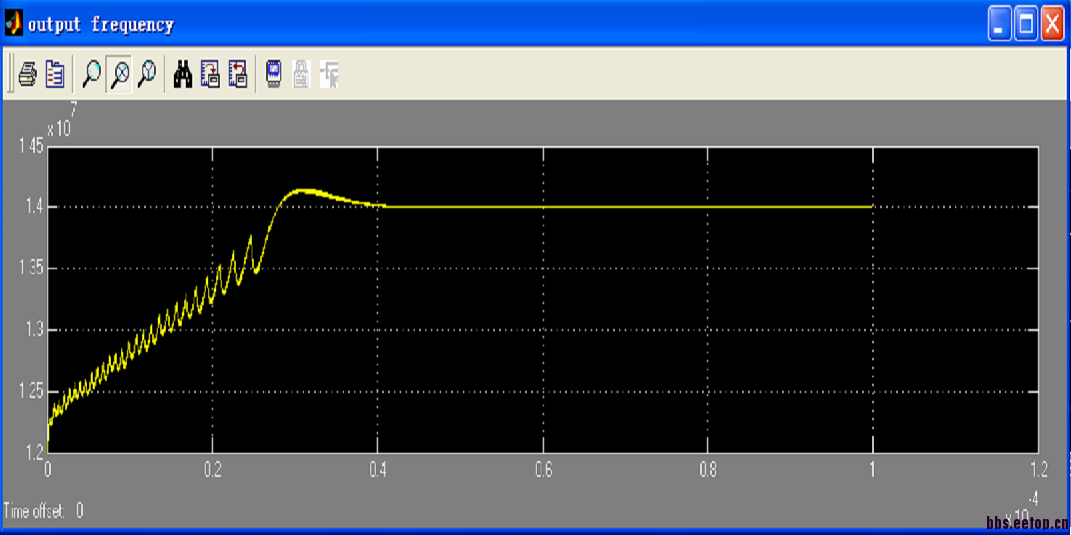

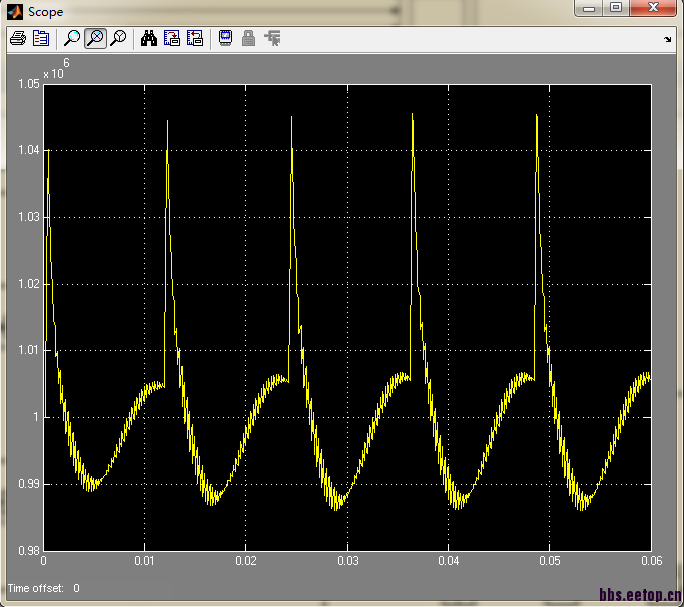

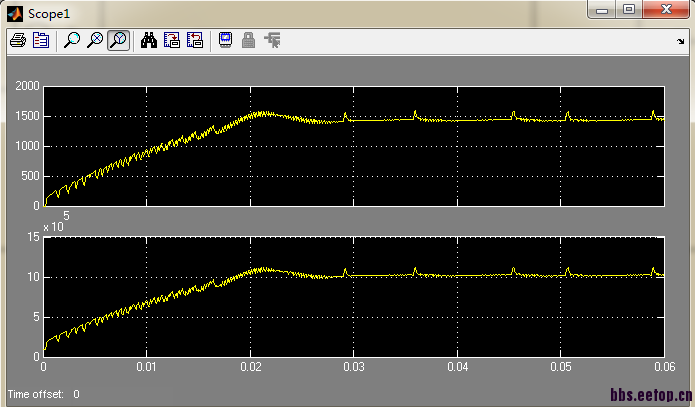

最后稳定的情况下VCO输出频率也不是完全的不变化吧,将稳定的直线放大可以看到还是在很小的范围波动,问题一:是否可以认为是几乎相当于不变的?

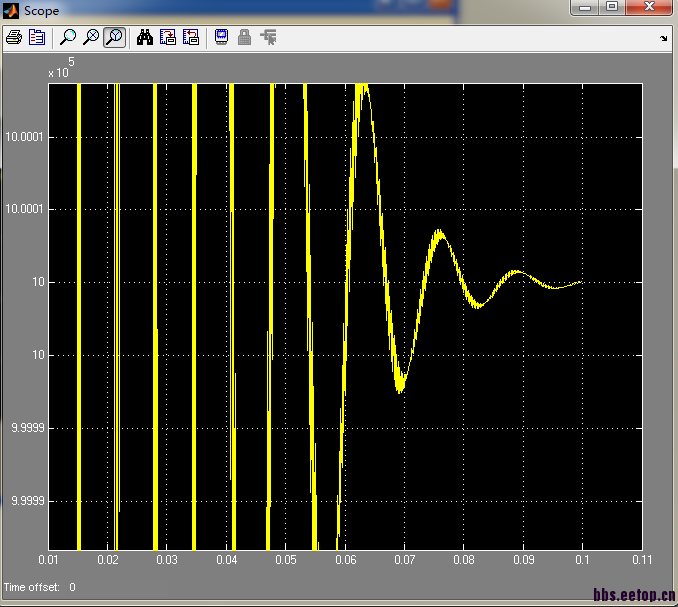

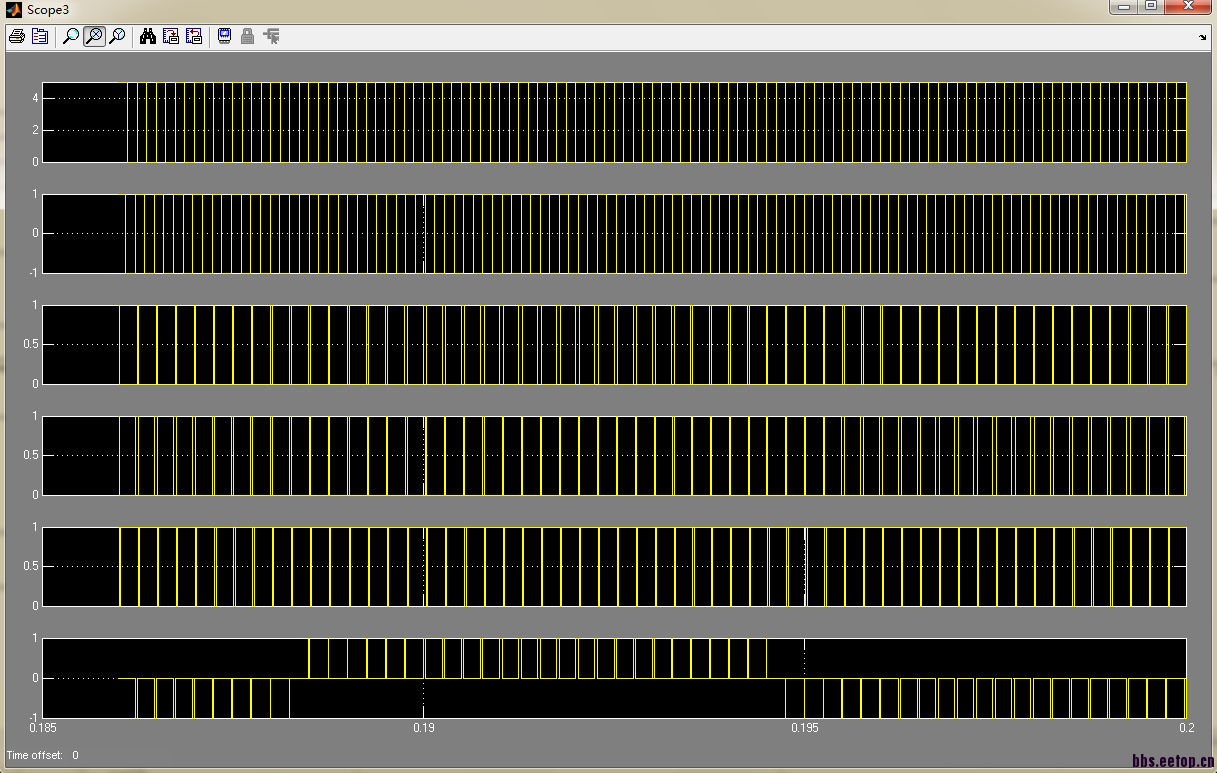

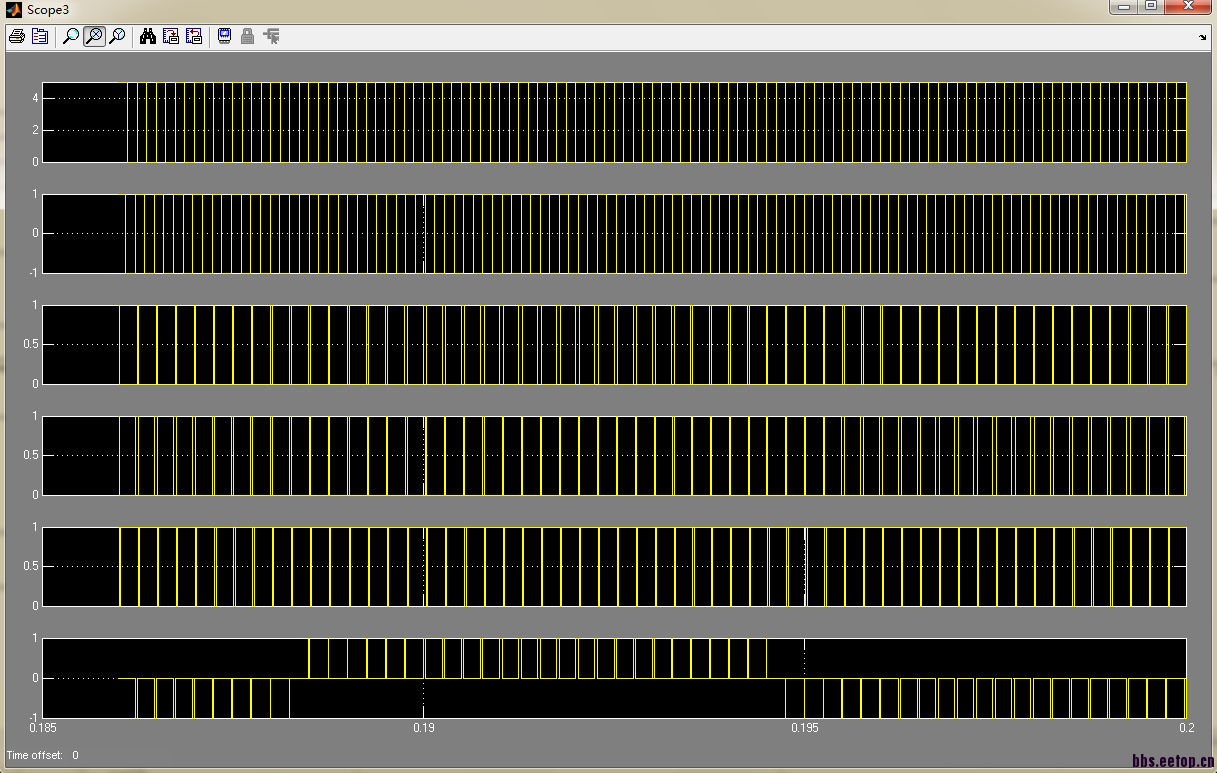

下图显示PDF输出和CP输出(最后一行)。其中CP的电流是在以很小的电流不断充电放电这个动态过程是否有问题?

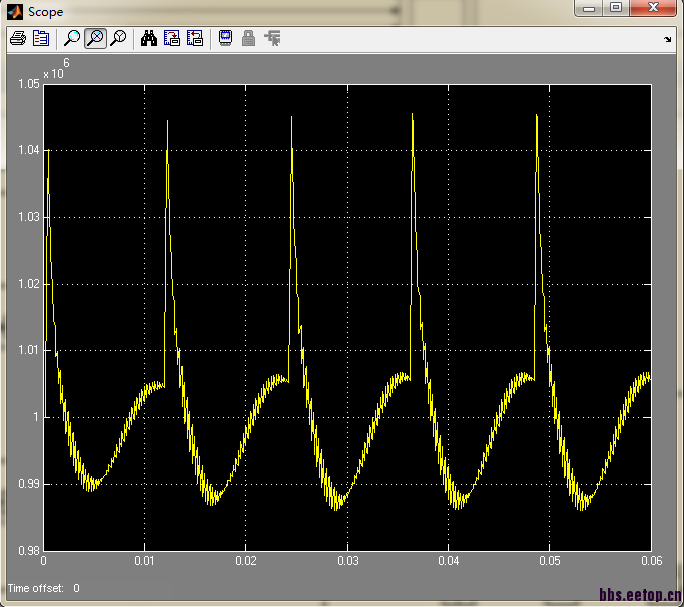

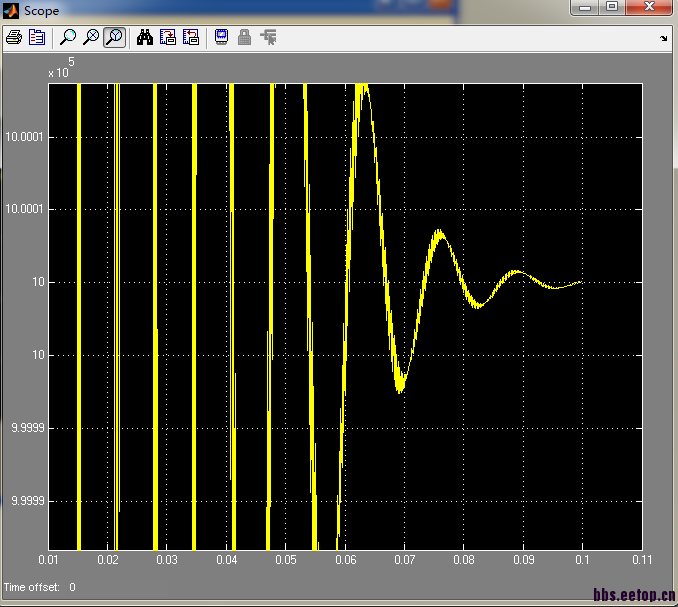

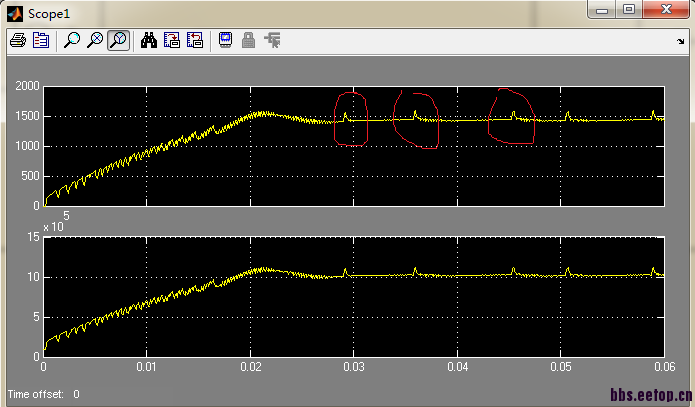

然后就是改变了延时参数之后会得到这样的图,当然是不正确的,原因是什么呢?特别是那个大的尖峰

最后的问题还是关于这种尖峰的,不过是稳定部分的,

。当然这个曲线不太好是因为LPF的参数设计的问题,改变那几个R1C1C2大小观察了下变化似乎不影响稳定阶段那几个小毛刺啊,是什么原因呢?

。当然这个曲线不太好是因为LPF的参数设计的问题,改变那几个R1C1C2大小观察了下变化似乎不影响稳定阶段那几个小毛刺啊,是什么原因呢?

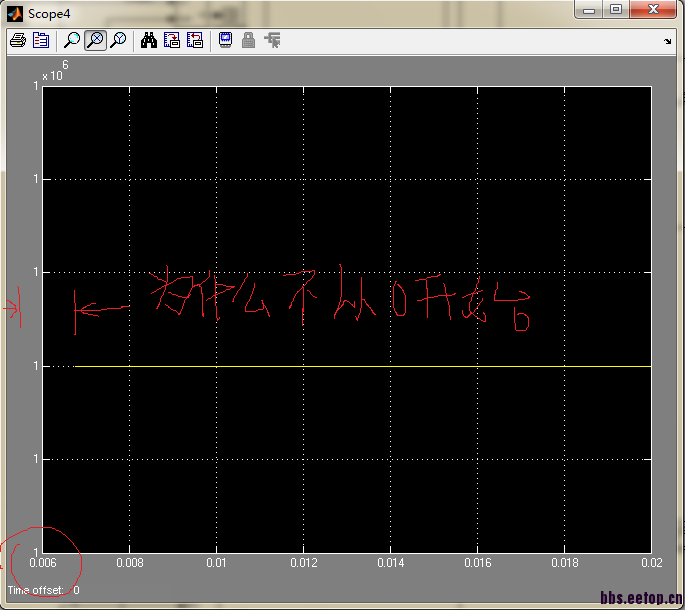

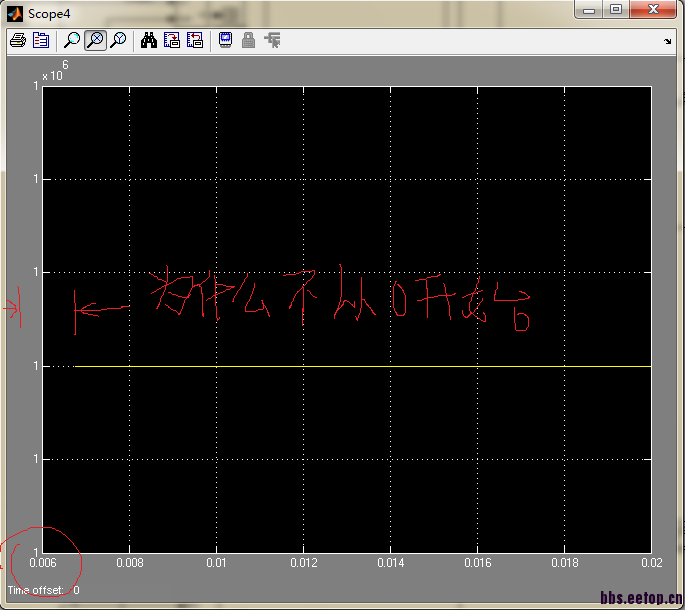

对了还有个关于仿真出波形的事情,为什么有时候仿真结果scope显示不是从0开始的,只是显示了很少一部分呢?比如说

在此谢过!

最后稳定的情况下VCO输出频率也不是完全的不变化吧,将稳定的直线放大可以看到还是在很小的范围波动,问题一:是否可以认为是几乎相当于不变的?

下图显示PDF输出和CP输出(最后一行)。其中CP的电流是在以很小的电流不断充电放电这个动态过程是否有问题?

然后就是改变了延时参数之后会得到这样的图,当然是不正确的,原因是什么呢?特别是那个大的尖峰

最后的问题还是关于这种尖峰的,不过是稳定部分的,

。当然这个曲线不太好是因为LPF的参数设计的问题,改变那几个R1C1C2大小观察了下变化似乎不影响稳定阶段那几个小毛刺啊,是什么原因呢?

。当然这个曲线不太好是因为LPF的参数设计的问题,改变那几个R1C1C2大小观察了下变化似乎不影响稳定阶段那几个小毛刺啊,是什么原因呢?对了还有个关于仿真出波形的事情,为什么有时候仿真结果scope显示不是从0开始的,只是显示了很少一部分呢?比如说

在此谢过!

分享下你的模型啊

之前论坛里分享貌似电科大那个老师的吧,就是最简单那种,

这种细节问题没人在意么,表沉

可以弱弱的问局,刚初学,怎么操作,怎么找到这些模块呢

抛砖引玉,pfd和chargepump 是哪个block

scope不显示0点的问题:scope左上侧第二个键,把限制最后5000点勾掉,看是不是这样?

我不是做CPPLL的,但是算抛砖引玉了。

第一个问题,锁相环锁相就是动态平衡的过程,因为PFD总会有个超前或者之后的信号,这就导致VCO频率的升高或降低,所以最后会有微小波动,这很正常,我们需要做的就是尽量减小这个波动。

第二个问题,你改变的延时是哪部分?改变环路延时是会出现锁定后波动变大的问题,我觉得这是因为环路延时相当于增加了一个环路延时所造成的相位偏差(也是我最近碰到的问题,感觉相位偏差可以近似等于对当前频率的积分,积分时间等于divIDER相位追上REF相位这个时间点到PFD输出信号传到VCO导致他改变这个时间点)感觉是由于这个相位偏差的存在导致你那个尖峰。

这是我粗浅的认识,希望各位前辈们多多指教,多多交流。

pulse的問題?