运放中有意义的话题

我的理解是降低折叠点出的小信号阻抗,因为从折叠点向共栅管源端向上看的小信号阻抗应该大于2/gm,折叠点向输入管看到的阻抗较大为1/gds,折叠点增加的二极管连接,相当于在该节点引入了并联的1/gm的阻抗,使得折叠点的阻抗进一步减小,有利于将该节点的pole推向更高的频率,增加GBW。当然还需要考虑增加的二极管连接实际上会增大折叠点的电容,也会影响到pole的移动。不过,应该会增加输出之路的静态电流,提高输出的SR。也会间接提高N管共栅级的DC电位,减小输出信号的摆幅。

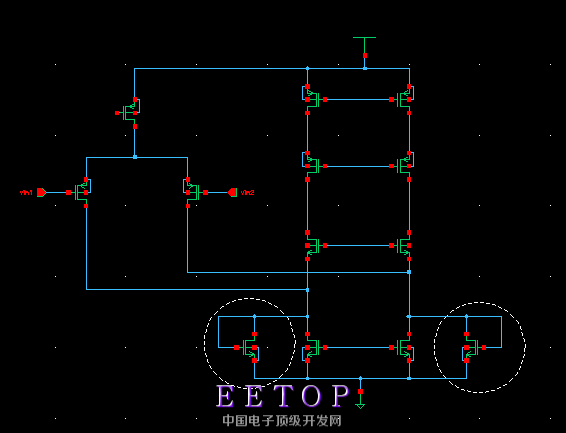

我的理解是这样的,现主要拿传统cascade、五管放大器和新结构cascade做对比。

对比与传统cascade:输入输出摆幅都少了一个Vth;享受不到cascade带来的增益提高;为不影响SR,需要额外的电流偏置diode管;但是优点是第二极点被推远,UGB会有改善。

对比与五管放大器:五管放大器输入输出摆幅互相限制,新结构没有;增益比五管放大器差不多,区别无非是五管输出阻抗是两个ro量级的并联,新结构只有一个ro量级的;新结构比五管放大器复杂,UGB应比五管的低。

纯属猜测,是不是利用和共栅管互补的特性改善不同工作点的一致性(环路稳定性maybe)。

如果小信号时,那两个管子是完全cutoff的,那就是防止输入大信号时,某点的电位升太高而把另一边完全关短

这两个二极管链接的器件L取值较大,在0.5um工艺中L=10um(这是反向解剖芯片看到的)

这两个二极管链接器件处于亚阈值导通,器件尺寸较大

这个不是很清楚,希望高手指点

猜不透设计这个电路人的意图

改善SR,钳位折叠点的电压,提高大信号响应速度,小信号特性不变。

值得一看

如果L较大,可能还是限制一下节点的电压,避免共栅管截止吧。

这有什么好分析的,就是两边并联了一个电阻,把折叠点的电位向下拉了一点而已。作用嘛,说不定就仅仅是因为designer太懒,不想改中间cascade管的nbias而已。

一提醒就明白了,3Q

降低增益