600V高压MOS管仿真经常不收敛是怎么回事?

时间:10-02

整理:3721RD

点击:

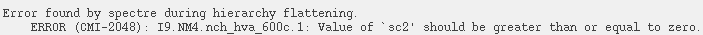

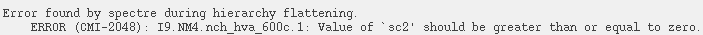

室温下,DC仿真收敛,可温度在40度以上就都不收敛;瞬态仿真也经常在特定条件下不收敛,报错都是下面内容:

SC2是什么参数?

SC2是什么参数?

SC2是什么参数?

SC2是什么参数?

一般是foundry的model做的不好。

在漏,栅极链接到地的大电阻。以不影响功能为准

方法1: drain先加个电阻试试1e7, 1e8,1e9, 形如下面

Electrode

{ Name="drain"Voltage=0.0Resistor=1e9}

方法2:Math 中改成下面形式

BreakCriteria{ Current(Contact="drain" AbsVal=1e-6) }

方法3:在process里,类似这样的自己加细网格在需要的区域, refinebox silicon min={x1y1}max= {x2 y2}xrefine= {0.02}add,慢慢尝试吧, 多看manual , 还有 physics里多加了不该加的模型也会不收敛的

ldmos ?

一般

跟

ic整合是 LDMOS .

不过独立mos 一般都

垂直的. 但电流比较大

,

问下高压

mos 都平袒画法

planar MOSFETwhy ?

好像trench vmos 或是umos

比较多使用

< 200v 多下

,

那

superJUNCTION MOS

为何会如此