请问CDR中的PI线性度仿真需要达到什么程度?

时间:10-02

整理:3721RD

点击:

请教一个问题,对CDR的PI仿真线性度,主要看DNL和INL,在tt情况,这两个指标需要达到什么值比较好呢?在多个corner情况下需要达到什么值呢?

顶一下

顶一下

顶一下

顶一下

对于PI来说,DNL比较重要。首先要保证单调性,高速应用比如20G以上不容易做好,一般偏差~0.3LSB就可以了。

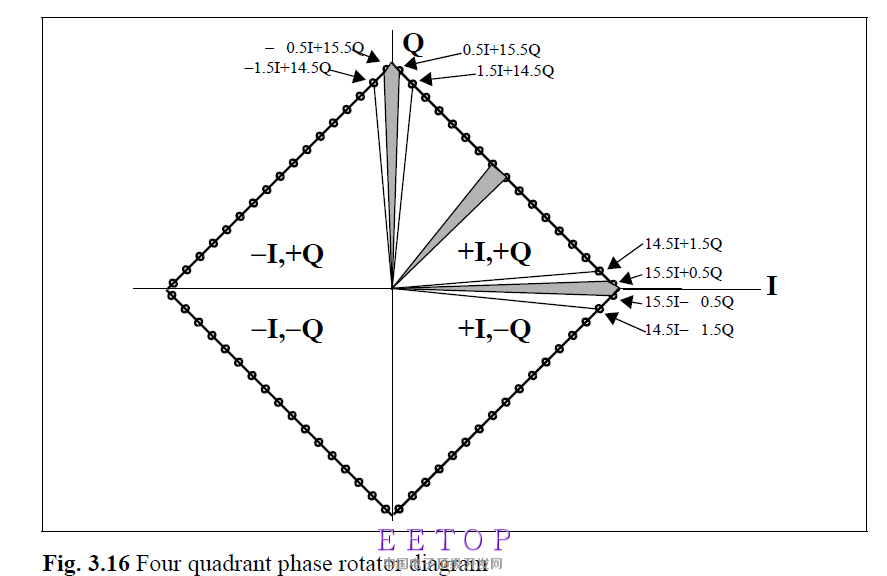

其实你PI bit/四边形or八边形架构一选定,PI理论上最小DNL和INL就已经出来了,在设计中朝着这个方向努力就行。再往top上看,PI的DNL/INL其实得根据CDR的system simulation来确定。一般DNL重要性高于INL,但高频INL的影响也不容忽视,设计中多注意跨象限PI线性度变化

非常感谢您,您说的~0.3LSB是包含了各种corner情况下的吗?仿DNL时输入的是方波时钟信号还是正弦波呢?

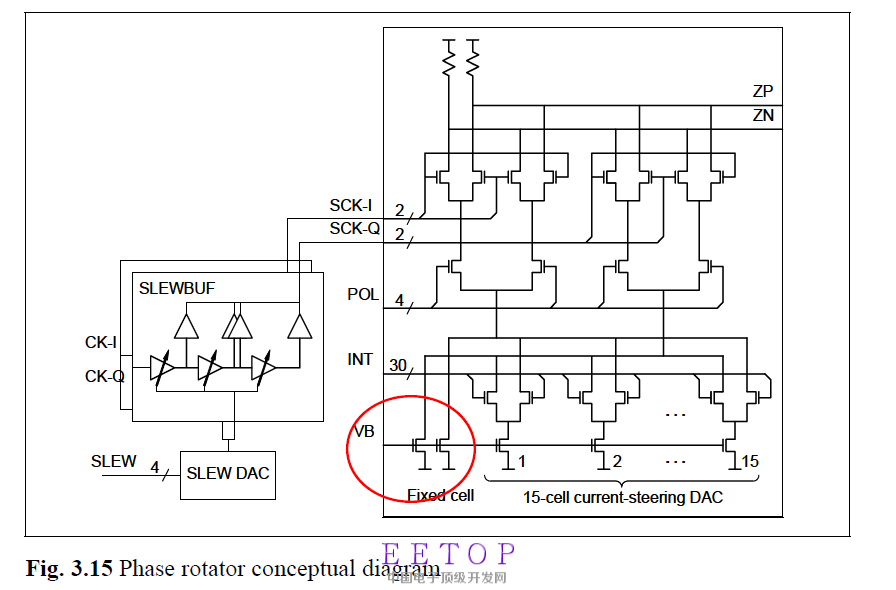

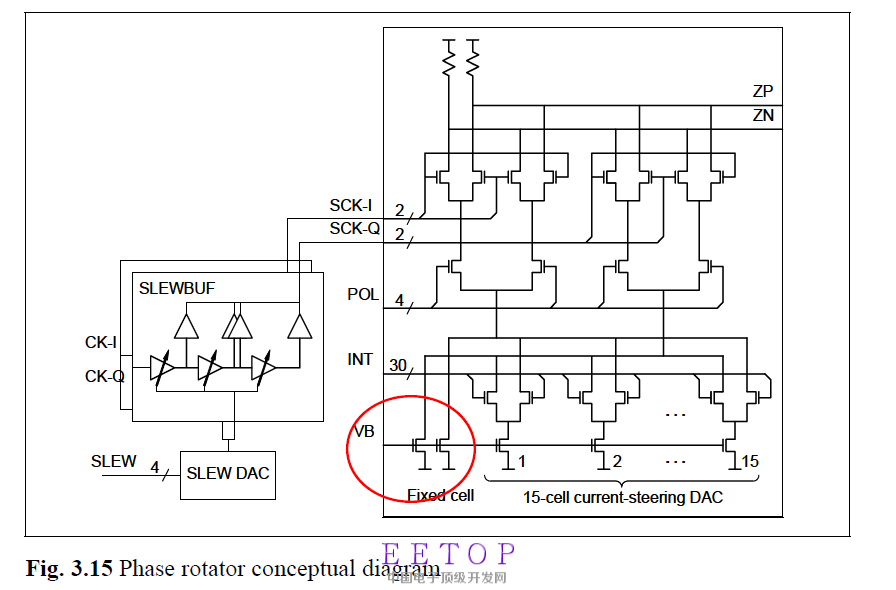

非常感谢您,您说的“PI bit/四边形or八边形架构一选定,PI理论上最小DNL和INL就已经出来了”,我没有理解,可以详细讲讲吗?您提醒的跨象限线性度的问题确实是非常好的提醒,我看到有的PI插值图起始相位不在坐标轴上,这样就避免了跨象限时出现的“跳码而相位不移动”的问题了吧?还有电路结构图,其中有个固定的电流之路,这个是电流型的PI。