请教高手cadence不收敛的问题

replace your fixed supply voltagewith a voltage ramp from 0V, most of cases can be solved.

解决办法

1. 查看你的step size是否足够精细,对于混合信号仿真,这可能导致结果不收敛

2.进入simulator options,将reltol vabstol isbstol三项的精度降低,考虑是可以降低微分方程的个数,具体是cadence的算法决定的,我也说不清楚,不过很好用。

二楼的方法管用。

那是初始工作点的问题。直接设置固定电压源有可能导致直流工作点不对。从0开始上升的电压也更符合实际情况。

.option runlvl 试一下!去掉电路中没用的dummy器件,百试不爽!

2楼的方法不错呢

我遇过同样的问题,问题是仿真时激励源的电压跳变时间太短,

2楼的意见 一般好用些。

折腾了几个小时,二楼的方法很有效,非常感谢!

学习了

2楼正解,我的就是这种情况!已解决!万分感谢

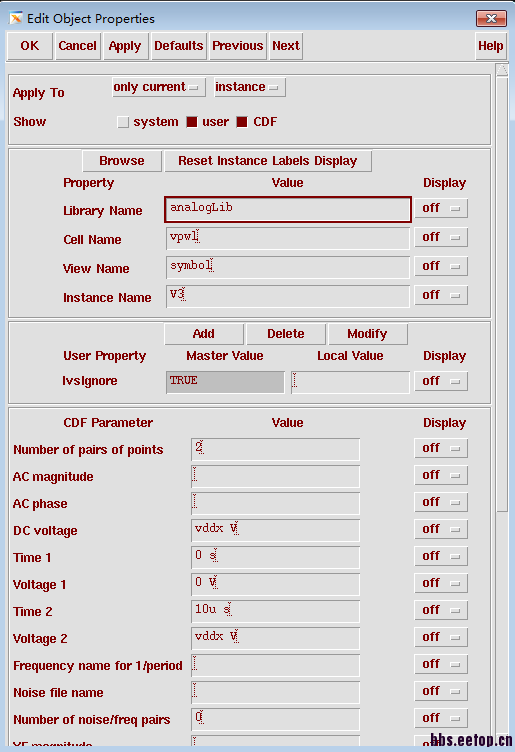

对二楼的方法不是很明白,不明白ramp说什么?可不可以解释下具体操作,非常感谢

2楼的方法赞的,多谢分享

你好,你是否是将电源替换成vpulse从0V上升到特定直流电压?个人这样尝试未解决问题

你好,你是否是将电源替换成vpulse从0V上升到特定直流电压?个人这样尝试未解决问题

就是电源电压给个斜坡信号,一般的都可以解决收敛问题

问题解决,2楼方法可行。谢谢。

二楼正解

2楼的方法,赞一下,解决了,谢谢!

三楼方法2实测也成功了!

请问,ahdllib中的opamp做成的迟滞比较器,出现了仿真不收敛的情况。怎么解决了 报错就是update too large,这个比较器的输入可能会遇到一定幅度的震荡