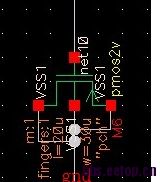

关于MOS电容的问题

1.如若用pmos来当电容,栅极为一端,S,D,B为另一端,而且这个电容的S,D,B是接地端的,那么,版图中,此pmos的N阱就变成了接到地(一般的pmos的N阱都是接高电位VDD),这样的话,从工艺上看,不就是很容易形成P衬底和此N阱的PN结正偏啦?应该会导致很大的电流吧?

2.如若用nmos来当电容,栅极为一端,S,D,B为另一端,那么从工艺上看,这个B端是不是就是整个衬底了,也就是整个硅片啦?那电容值怎么算呢?

不知道我的理解有没有错,大家一起讨论一下。

1. (如果地是最低电位)是,绝对不能那么做;不过可以把pmos的S.D.B端接最高电位,gate端接较低电位;

2.如果想用nmos做电容,需要有隔离的pwell,这样电容的两端分别是nmos的gate和S.D.B.;如果没有隔离的pwell, nmos的bulk 是和p-sub短接的,那样的电容毫无意义

学习了

谢谢你的回复!

1.也就是说要是用NMOS来做电容的话,G端都是接较低电平,而D,S,B端都是接较高电平是吗?

我的这个电容两端,没有一端可以接到最高电平VDD,这样会不会有什么影响呢?貌似上面提到的这个寄生的PN结,其正向电压也是小于等于0的。

2.PMOS做电容的话,没有隔离的P-WELL,是做不成的?是这个意思吗?

你正好说反了,1是pmos, 2是nmos

针对p-sub、n-well单阱工艺

1、PMOS做电容,如果是独立的nwell,那么SBD接地不会出现PN结正偏问题(当然前提是你的p-sub接最低电位);另外我想问的是既然PMOS电容有一端接地,干脆选择G端就OK啦,这样也就不用纠结啊?

2、NMOS电容如果不是双阱工艺,那么无需考虑,因为你只有一种选择---B端必须接最低电位

电容计算公式:C=ε *ε0* S/d;

式中:

电容C,单位F;

ε相对介电常数(SiO2介电常数);

ε0真空介电常数8.86×10(-12方)单位F/m;

面积S,单位平方米;

极板间距d(栅氧厚度),单位米;

谢谢回复!

那么,如果我用nmos的话,这个B端就是整个衬底了,那公式中的面积S该怎么算?怎么感觉这个怪怪的。

或者这个S不是衬底的整个面积?

电容是由两个极板产生的,S当然由最小的一极决定,也就是由栅极决定的,不过NMOS做电容的话BSD一端一点过要接地,PMOS做电容也可以,BSD接一起不会有PN结导通(瞬态响应除外)

mos电容的使用,要看wafer的type

如果是P-sub wafer,那么nwell是可以接任意电位的(不要低于p-sub的电位),此时只要把不同电位的nwell分开就行了

如果是n-sub wafer,就刚好相反

以p-sub wafer为例

nmos电容的S/D/B只能接在最低电位上,所以限制了nmos电容的使用

pmos电容的S/D/B, 可以接任意电位(nwell>=0V就行),所以使用更灵活

mos 电容会受偏置电压和信号频率的影响

在使用的时候,尽量使两极板的电压差大于Vt,此时mos的电容值主要取决于gate面积

学习了!

nice...

xue ix lexiexie

不是计算整个衬底的面积哦。应该只要计算耗尽层面积就行,分三部分,沟道耗尽层,D极耗尽层,S极耗尽层,还要分侧面底面。

增强型MOS管加偏压小了还不会反型,对容量影响很大。

建议使用耗尽管,偏压至少可以到零电压。

电容的有效面积为上下极板的重叠部分!

回复回复。

学习了~

bulk 与psub短接,这样的电容为什么毫无意义?

学习一下 谢谢啦

nmos管做电容,电容公式为C=ε *ε0* S/d,其中S可以通宽长来计算,那么d怎么得到呢?

学习啦~

right!

学习了

那电路中既然可以调用任意值大小的电容,为什么还需要构造MOS电容?理由是什么呢?(我不太明白这样的运用方式),谢谢解答!

理由就是mos电容的密度更大,可以用更小的面积实现更大电容。

psub的工艺能不能把NMOS做到NWELL里面,然后把NMOS的S/B/D接VDD。

即使正偏,也流不到哪儿去、

Good!