cadence ies12.20.003 安装license问题,求各路英雄指点

时间:10-02

整理:3721RD

点击:

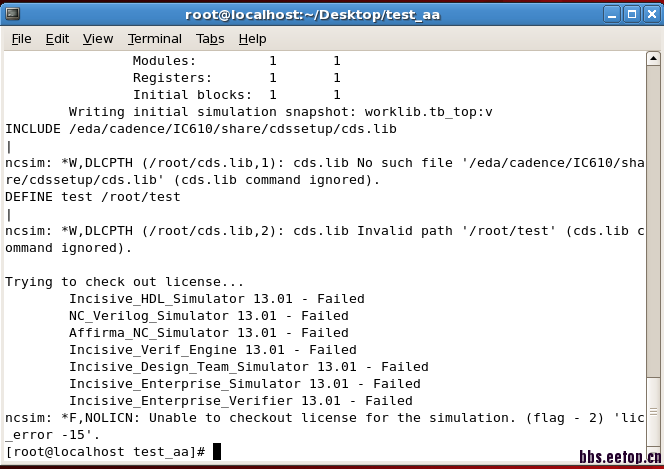

各路豪杰们,小弟在安装ies12.20.003时遇到ncsim没有lciense,具体现象如下,求名医指点哦:

1. 运行 irun +access+wr tb_top.v 提示如下错误:

2. .bashrc 配置如下:

3. 系统环境如下:

4. 运行 lmgrd -c $LM_LICENSE_FILE -l ius1220003_lic.log 产生如下图log,且log文件一直在变大,查看似乎是相同的东东一直在循环:

15:47:31 (lmgrd) -----------------------------------------------

15:47:31 (lmgrd)Please Note:

15:47:31 (lmgrd)

15:47:31 (lmgrd)This log is intended for debug purposes only.

15:47:31 (lmgrd)In order to capture accurate license

15:47:31 (lmgrd)usage data into an organized repository,

15:47:31 (lmgrd)please enable report logging. Use Macrovision's

15:47:31 (lmgrd)software license administrationsolution,

15:47:31 (lmgrd)FLEXnet Manager, toreadily gain visibility

15:47:31 (lmgrd)into license usage data and to create

15:47:31 (lmgrd)insightful reports on critical information like

15:47:31 (lmgrd)license availability and usage. FLEXnet Manager

15:47:31 (lmgrd)can be fully automated to run these reports on

15:47:31 (lmgrd)schedule and can be used to track license

15:47:31 (lmgrd)servers and usage across a heterogeneous

15:47:31 (lmgrd)network of servers including Windows NT, Linux

15:47:31 (lmgrd)and UNIX. Contact Macrovision at

15:47:31 (lmgrd)www.macrovision.com for more details on how to

15:47:31 (lmgrd)obtain an evaluation copy of FLEXnet Manager

15:47:31 (lmgrd)for your enterprise.

15:47:31 (lmgrd)

15:47:31 (lmgrd) -----------------------------------------------

15:47:31 (lmgrd)

15:47:31 (lmgrd)

15:47:31 (lmgrd) The license server manager (lmgrd) running as root:

15:47:31 (lmgrd)

This is a potential security problem

15:47:31 (lmgrd)

and is not recommended.

15:47:31 (lmgrd) FLEXnet Licensing (v10.8.2.1 build 30341) started on localhost.localdomain (linux) (12/21/2014)

15:47:31 (lmgrd) Copyright (c) 1988-2006 Macrovision Europe Ltd. and/or Macrovision Corporation. All Rights Reserved.

15:47:31 (lmgrd) US Patents 5,390,297 and 5,671,412.

15:47:31 (lmgrd) World Wide Web:http://www.macrovision.com

15:47:31 (lmgrd) License file(s): /eda/cadence/license/ius12_20_003_lic.dat

15:47:31 (lmgrd) lmgrd tcp-port 26000

15:47:31 (lmgrd) Starting vendor daemons ...

15:47:31 (cdslmd) FLEXnet Licensing version v10.8.2.1 build 30341

15:47:31 (lmgrd) Started cdslmd (internet tcp_port 47838 pid 4925)

15:47:32 (cdslmd) Server started on localhost.localdomain for:

100

15:47:32 (cdslmd) 111

11300

11400

15:47:32 (cdslmd) 11701

11702

11703

15:47:32 (cdslmd) 11710

12110

12111

15:47:32 (cdslmd) 12121

12141

12141_64bit

15:47:32 (cdslmd) 12150

12500

14000

15:47:32 (cdslmd) 14010

14020

14030

15:47:32 (cdslmd) 14040

14060

14100

15:47:32 (cdslmd) 14101

14110

14111

15:47:32 (cdslmd) 14120

14130

14140

15:47:32 (cdslmd) 14400

14410

14420

15:47:32 (cdslmd) 200

20120

20121

15:47:32 (cdslmd) 20122

20123

20124

15:47:32 (cdslmd) 20127

20128

20220

15:47:32 (cdslmd) 20221

20222

20227

15:47:32 (cdslmd) 206

207

21000

15:47:32 (cdslmd) 21060

21200

21400

15:47:32 (cdslmd) 2141

_21900

21900

15:47:32 (cdslmd) 21920

223

224

15:47:32 (cdslmd) 22650

22800

22810

15:47:32 (cdslmd) 24015

24025

24100

15:47:32 (cdslmd) 24205

250

251

15:47:32 (cdslmd) 26000

274

276

15:47:32 (cdslmd) 278

279

283

15:47:32 (cdslmd) 300

3000

3001

15:47:32 (cdslmd) 30010

3002

300_64bit

15:47:32 (cdslmd) 3011

302

305

15:47:32 (cdslmd) 31000

311

3111

15:47:32 (cdslmd) 312

314

316

15:47:32 (cdslmd) 318

32015

32100

15:47:32 (cdslmd) 32101

32110

32120

15:47:32 (cdslmd) 32125

32130

32140

15:47:32 (cdslmd) 32150

32190

322

15:47:32 (cdslmd) 32500

32501

32502

15:47:32 (cdslmd) 32503

32505

32510

15:47:32 (cdslmd) 32520

32521

32530

15:47:32 (cdslmd) 32550

32600

32610

15:47:32 (cdslmd) 32620

32630

32640

15:47:32 (cdslmd) 32760

33000

33010

15:47:32 (cdslmd) 33011

33015

33016

15:47:32 (cdslmd) 33100

33300

33301

15:47:32 (cdslmd) 334

33500

33580

15:47:32 (cdslmd) 336

3405

34500

15:47:32 (cdslmd) 34510

34511

34530

15:47:32 (cdslmd) 34570

34580

35100

15:47:32 (cdslmd) 35200

360

362

15:47:32 (cdslmd) 365

365_64bit

370

15:47:32 (cdslmd) 371

37100

373

15:47:32 (cdslmd) 374

38500

38520

15:47:32 (cdslmd) 39000

39001

3D_FieldSolver_Engine

15:47:32 (cdslmd) 4000

40020

40030

15:47:32 (cdslmd) 40040

40500

41000

15:47:32 (cdslmd) 50000

50010

501

15:47:32 (cdslmd) 50110

50200

502A

15:47:32 (cdslmd) 5100

51022

51023

15:47:32 (cdslmd) 51060

51070

51170

15:47:32 (cdslmd) 550

570

61300

15:47:32 (cdslmd) 61400

681

7000

15:47:32 (cdslmd) 70000

70110

70110_64bit

15:47:32 (cdslmd) 70120

70120_64bit

70130

15:47:32 (cdslmd) 70510

70510_64_bit

70520

15:47:32 (cdslmd) 70520_64bit

71110

71110_64bit

15:47:32 (cdslmd) 71120

71130

71510

15:47:32 (cdslmd) 71520

72110

72120

15:47:32 (cdslmd) 72130

72131

72132

15:47:32 (cdslmd) 72133

72134

72135

15:47:32 (cdslmd) 72140

72150

727

15:47:32 (cdslmd) 728

729

730

15:47:32 (cdslmd) 730_64bit

733

73510

15:47:32 (cdslmd) 73520

761

780

15:47:32 (cdslmd) 780_64bit

900

9000

15:47:32 (cdslmd) 90001

920

940

15:47:32 (cdslmd) 945

950

95100

15:47:32 (cdslmd) 95115

95120

952

15:47:32 (cdslmd) 95200

95210

95220

15:47:32 (cdslmd) 95255

95300

95310

15:47:32 (cdslmd) 95320

95400

960

15:47:32 (cdslmd) 960_64bit

963

964

15:47:32 (cdslmd) 965

966

972

15:47:32 (cdslmd) 974

991

992

15:47:32 (cdslmd) 993

994

995

15:47:32 (cdslmd) a2dxf

aae-signalscan

aae-signalscan-transaction

15:47:32 (cdslmd) aae-transaction-explorer ABIT

Actel_FPGA

15:47:32 (cdslmd) actomd

ADE_ElectronStorm_Option ADE_VoltageStorm_Option

15:47:32 (cdslmd) ADV_2S10PUC_ALL ADV_2S15PUC_ALL ADV_2S20PUC_ALL

15:47:32 (cdslmd) ADV_2S40PUC_ALL ADV_2S60PUC_ALL ADV_2SUPUC_ALL

15:47:32 (cdslmd) ADV_4S10PUC_ALL ADV_4S20PUC_ALL ADV_4S40PUC_ALL

15:47:32 (cdslmd) ADV_4S60PUC_ALL ADV_4SUPUC_ALL

ADV_6S60PUC_ALL

15:47:32 (cdslmd) ADV_6S90PUC_ALL ADV_6SUPUC_ALL

Advanced_Cell_Placer

15:47:32 (cdslmd) advanced_package_designer Advanced_Pkg_Engineer_3D adv_package_designer_expert

15:47:32 (cdslmd) adv_package_engineer_expert Affirma_3rdParty_Sim_Interface Affirma_advanced_analysis_env

15:47:32 (cdslmd) Affirma_AMS_distrib_processing Affirma_ams_simulator Affirma_equivalence_checker

15:47:32 (cdslmd) Affirma_equiv_checker_prep Affirma_model_checker Affirma_model_packager_export

15:47:32 (cdslmd) Affirma_NC_Simulator Affirma_NC_VHDL_Desktop_Sim Affirma_RF_IC_package

15:47:32 (cdslmd) Affirma_RF_IC_package_modeler Affirma_RF_SPW_model_link affirma-signalscan

15:47:32 (cdslmd) affirma-signalscan-control affirma-signalscan-pro affirma-signalscan-schmatic

15:47:32 (cdslmd) affirma-signalscan-source affirma-signalscan-transaction Affirma_sim_analysis_env

15:47:32 (cdslmd) Affirma_transaction_analysis affirma-transaction-explorer Affirma_trans_logic_abstracter

15:47:32 (cdslmd) ALL_EBD

Allegro_CAD_Interface Allegro_Design_Editor_620

15:47:32 (cdslmd) Allegro_Designer Allegro_designer_suite Allegro_design_expert

15:47:32 (cdslmd) allegro_dfa

allegro_dfa_att Allegro_Expert

15:47:32 (cdslmd) Allegro_Librarian allegro_non_partner Allegro_Package_Designer_620

15:47:32 (cdslmd) Allegro_Package_SI_620 Allegro_Package_SI_620_Suite Allegro_PCB

15:47:32 (cdslmd) Allegro_PCB_Design_230 Allegro_PCB_Design_620 Allegro_PCB_Interface

15:47:32 (cdslmd) Allegro_PCB_Partitioning Allegro_PCB_RF

Allegro_PCB_Router_210

15:47:32 (cdslmd) Allegro_PCB_Router_230 Allegro_PCB_Router_610 Allegro_PCB_SI_230

15:47:32 (cdslmd) Allegro_PCB_SI_620 Allegro_PCB_SI_630 Allegro_PCB_SI_630_Suite

15:47:32 (cdslmd) Allegro_performance Allegro_Pkg_Designer_620_Suite allegroprance

15:47:32 (cdslmd) Allegro_studio

allegro_symbol

Allegro_Viewer_Plus

15:47:32 (cdslmd) Altera_MAX

Ambit_BuildGates Ambit_libcompile

15:47:32 (cdslmd) Ambit_RnD_option AMD_MACH

AmoebaPlace

15:47:32 (cdslmd) AMS_Designer_Link AMS_environment AMS_Methodology_Kit

15:47:32 (cdslmd) AMS_Option_to_Incisive Analog_Design_Environment_GXL Analog_Design_Environment_L

15:47:32 (cdslmd) Analog_Design_Environment_XL ANALOG_WORKBENCH APD

15:47:32 (cdslmd) Aptivia

archiver

arouter

15:47:32 (cdslmd) Artist_Optimizer Artist_Statistics Assura_DRC

15:47:32 (cdslmd) Assura_DV_design_rule_checker Assura_DV_LVS_checker Assura_DV_parasitic_extractor

15:47:32 (cdslmd) Assura_LVS

Assura_MP

Assura_OPC

15:47:32 (cdslmd) Assura_RCX

Assura_RCX_Adv_Process Assura_RCX-FS

15:47:32 (cdslmd) Assura_RCX-HF

Assura_RCX-MP

Assura_RCX-PL

15:47:32 (cdslmd) Assura_SI

Assura_SiMC

Assura_SI-TL

15:47:32 (cdslmd) Assura_SiVL

Assura_UI

Atmel_ATV

15:47:32 (cdslmd) AWB_Batch

AWB_BEHAVIOR

AWB_DIST_SIM

15:47:32 (cdslmd) AWB_MAGAZINE

AWB_MAGNETICS

AWB_MIX

15:47:32 (cdslmd) AWB_PPLOT

AWB_RESOLVE_OPT AWB_SIMULATOR

15:47:32 (cdslmd) AWB_SMOKE

AWB_SPICEPLUS

AWB_STATS

15:47:32 (cdslmd) Base_Digital_Body_Lib Base_Verilog_Lib BG

15:47:32 (cdslmd) BlockMaster_Characterizer BlockMaster_Optimizer BlockPlace

15:47:32 (cdslmd) BoardQuest_Designer BoardQuest_Team BOGUS

15:47:32 (cdslmd) BRDST_IF

BuildGates_Extreme Cadence_3D_Design_Viewer

15:47:32 (cdslmd) Cadence_chip_assembly_router CADIF_IF

caeviews

15:47:32 (cdslmd) cals_out

Capture

CaptureCIS

15:47:32 (cdslmd) Capture_CIS_Studio catia

cbds_in

15:47:32 (cdslmd) CCAR

CDMA_Simulation_Runtime cdxe_in

15:47:32 (cdslmd) CELL3

CELL3_ARO

CELL3_CROSSTALK

15:47:32 (cdslmd) CELL3_CTS

CELL3_DIST

CELL3_ECL

15:47:32 (cdslmd) CELL3_OPENDEV

CELL3_OPENEXE

CELL3_PA

15:47:32 (cdslmd) CELL3_PR

CELL3_QPLACE

CELL3_QPLACE_TIMING

15:47:32 (cdslmd) CELL3_QROUTE

CELL3_RGT

CELL3_SCAN

15:47:32 (cdslmd) CELL3_TIMING

CELL3_WIDEWIRE

celtic

15:47:32 (cdslmd) Celtic_Crosstalk_Analyzer Celtic_NDC

CHDL_DesignAccess

15:47:32 (cdslmd) CheckADV_ALL

CheckPlus

Checkplus_Expert

15:47:32 (cdslmd) Cierto_HW_design_sys_2000 Cierto_signal_proc_wrksys_2000 Cierto_SPW_CDMA_Library

15:47:32 (cdslmd) Cierto_SPW_comm_lib_flt_pt Cierto_SPW_comm_library_fxp_pt Cierto_SPW_GSM_VE

15:47:32 (cdslmd) Cierto_SPW_IS136_VE Cierto_SPW_link_to_Ambit_BG Cierto_SPW_link_to_NC_sim

15:47:32 (cdslmd) Cierto_SPW_model_manager Cierto_SPW_multimedia_kit Cierto_SPW_pcscdma_VE

15:47:32 (cdslmd) Cierto_Wireless_LAN_Library ClockSyn

Clock_Tree_Generation

15:47:32 (cdslmd) Cobra_Simulator comp

compose

15:47:32 (cdslmd) compose_autoplan compose_gcr

ComposerCheckPlus_AdvRules

15:47:32 (cdslmd) ComposerCheckPlus_Checker ComposerCheckPlus_RuleDev Composer_EDIF300_Connectivity

15:47:32 (cdslmd) Composer_EDIF300_Schematic Composer_Schematic_Generator Composer_Spectre_Sim_Solution

15:47:32 (cdslmd) compose_scells

compose_tlmr

compose_util

15:47:32 (cdslmd) concept

ConceptHDL

Concept_HDL_expert

15:47:32 (cdslmd) Concept_HDL_rules_checker Concept_HDL_studio conceptXPC

15:47:32 (cdslmd) ConcICe_Option

Conformal_Asic

Conformal_Constraint_Designer

15:47:32 (cdslmd) Conformal_Constraint_Dsgnr_XL Conformal_Custom conformal_datapath

15:47:32 (cdslmd) Conformal_ECO

Conformal_ECO_GXL Conformal_GXL

15:47:32 (cdslmd) conformal_ldd

conformal_lec

Conformal_Low_Power

15:47:32 (cdslmd) Conformal_Low_Power_GXL Conformal_LP_GXL conformal_lvr

15:47:32 (cdslmd) conformal_mem

Conformal_Ultra conformal_vhd

15:47:32 (cdslmd) conformal_vlg

Corners_Analysis cpe

15:47:32 (cdslmd) CP_Ele_Checks

CPF

cpte

15:47:32 (cdslmd) CPtoolkit

crefer

CTE

15:47:32 (cdslmd) cvtomd

CWAVES

CWB01

15:47:32 (cdslmd) CWB03

CWB04

CWB05

15:47:32 (cdslmd) Datapath_Preview_Option Datapath_Verilog Datapath_VHDL

15:47:32 (cdslmd) debug

DelayCal

DesignViewer

15:47:32 (cdslmd) Desktop_mgr

Device_Level_Placer Device_Level_Router

15:47:32 (cdslmd) DFM_2S10PUC_ALL DFM_2S15PUC_ALL DFM_2S20PUC_ALL

15:47:32 (cdslmd) DFM_2S40PUC_ALL DFM_2S60PUC_ALL DFM_2SUPUC_ALL

15:47:32 (cdslmd) DFM_4S10PUC_ALL DFM_4S20PUC_ALL DFM_4S40PUC_ALL

15:47:32 (cdslmd) DFM_4S60PUC_ALL DFM_4SUPUC_ALL

DFM_6S60PUC_ALL

15:47:32 (cdslmd) DFM_6S90PUC_ALL DFM_6SUPUC_ALL

DFM_Core_Technology

15:47:32 (cdslmd) dfsverifault

DISCRETE_LIB

Distributed_Dracula_Option

15:47:32 (cdslmd) DRAC2CORE

DRAC2DRC

DRAC2LVS

15:47:32 (cdslmd) DRAC3CORE

DRAC3DRC

DRAC3LVS

15:47:32 (cdslmd) DRACACCESS

DRACDIST

DRACERC

15:47:32 (cdslmd) DRACLAYDE

DRACLPE

DRACLVS

15:47:32 (cdslmd) DRACPG_E

DRACPLOT

DRACPRE

15:47:32 (cdslmd) DRACSLAVE

dracula_in

dxf2a

15:47:32 (cdslmd) e2v

EB_2S10PUC_ALL

EB_2S15PUC_ALL

15:47:32 (cdslmd) EB_2S20PUC_ALL

EB_2S40PUC_ALL

EB_2S60PUC_ALL

15:47:32 (cdslmd) EB_2SUPUC_ALL

EB_4S10PUC_ALL

EB_4S20PUC_ALL

15:47:32 (cdslmd) EB_4S40PUC_ALL

EB_4S60PUC_ALL

EB_4SUPUC_ALL

15:47:32 (cdslmd) EB_6S60PUC_ALL

EB_6S90PUC_ALL

EB_6SUPUC_ALL

15:47:32 (cdslmd) EBD_edit

EBD_floorplan

EBD_power

15:47:32 (cdslmd) eCapture

ECO

edif2ged

15:47:32 (cdslmd) EDIF_Netlist_Interface EDIF_Schematic_Interface EditBase

15:47:32 (cdslmd) EditBase_ALL

EditFST

EditFST_ALL

15:47:32 (cdslmd) EditPlace_ALL

EditRoute_ALL

EF_2SUPUC_ALL

15:47:32 (cdslmd) EF_4S40PUC_ALL

EF_4S60PUC_ALL

EF_4SUPUC_ALL

15:47:32 (cdslmd) EF_6S60PUC_ALL

EF_6S90PUC_ALL

EF_6SUPUC_ALL

15:47:32 (cdslmd) EMCdisplay

EMControl

EMControl_Float

15:47:32 (cdslmd) EMI_ALL

Encounter

Encounter_Adv_Node_GXL

15:47:32 (cdslmd) Encounter_C

Encounter_ClockSyn Encounter_Digital_Impl_Sys_L

15:47:32 (cdslmd) Encounter_Digital_Impl_Sys_XL Encounter_Low_Power_GXL Encounter_Mixed_Signal_GXL

15:47:32 (cdslmd) Encounter_QRC_Extraction_GXL Encounter_QRC_Extraction_L Encounter_QRC_Extraction_XL

15:47:32 (cdslmd) Encounter_Test_Architect Encounter_Timing_System_L Encounter_Timing_System_XL

15:47:32 (cdslmd) Encounter_True_Time Encounter_Wave_Viewer Encounter_X

15:47:32 (cdslmd) Envisia_DataPath_option Envisia_GE_ultra_place_route Envisia_LowPower_option

15:47:32 (cdslmd) Envisia_PKS

Envisia_RAC

Envisia_SE_SI_place_route

15:47:32 (cdslmd) Envisia_SE_ultra_place_route Envisia_Utility evc_verisity_ahb

15:47:32 (cdslmd) evc_verisity_axi evc_verisity_enet evc_verisity_pci

15:47:32 (cdslmd) evc_verisity_pcie evc_verisity_pcie_ep evc_verisity_pcie_rc

15:47:32 (cdslmd) evc_verisity_usb evc_verisity_usb_otg expert

15:47:32 (cdslmd) expgen

explorer

Express

15:47:32 (cdslmd) ExpressPlus

Extended_Digital_Body_Lib Extended_Digital_Lib

15:47:32 (cdslmd) Extended_Verilog_Lib fcengine

fcheck

15:47:32 (cdslmd) FE_ASIC

FE_ASIC_Agere

FE_ASIC_Fujitsu

15:47:32 (cdslmd) FE_ASIC_IBM

FE_ASIC_LSILogic FE_ASIC_Mitsubishi

15:47:32 (cdslmd) FE_ASIC_NEC

FE_ASIC_Philips FE_ASIC_Samsung

15:47:32 (cdslmd) FE_ASIC_ST

FE_ASIC_TI

FE_ASIC_Toshiba

15:47:32 (cdslmd) FE_Classic

FE_GPS

fethman

15:47:32 (cdslmd) fetsetup

FE_Ultra

Fire_Ice_Cell

15:47:32 (cdslmd) Fire_Ice_Cell_Transistor Fire_IceQXC2_Cell Fire_Parallel

15:47:32 (cdslmd) FirstEncounter

First_Encounter_GPS First_Encounter_GXL

15:47:32 (cdslmd) FirstEncounterSOC First_Encounter_Ultra First_Encounter_VIP

15:47:32 (cdslmd) First_Encounter_XL FloatPC_ALL

FloorPlan

15:47:32 (cdslmd) fluke

FPGA_Flows

FPGA_OPTIMIZER

15:47:32 (cdslmd) FPGA_Tools

Framework

fsim

15:47:32 (cdslmd) FST_2SUPUC_ALL

FST_4S40PUC_ALL FST_4S60PUC_ALL

15:47:32 (cdslmd) FST_4SUPUC_ALL

FST_6S60PUC_ALL FST_6S90PUC_ALL

15:47:32 (cdslmd) FST_6SUPUC_ALL

FUNCTION_LIB

GATEENSEMBLE

15:47:32 (cdslmd) GATEENSEMBLE_ARO GATEENSEMBLE_CROSSTALK GATEENSEMBLE_CTS

15:47:32 (cdslmd) GATEENSEMBLE_CTS_LE GATEENSEMBLE_CTS_UL GATEENSEMBLE_DIST

15:47:32 (cdslmd) Gate_Ensemble_DSM Gate_Ensemble_DSM_Crosstalk GATEENSEMBLE_ECL

15:47:32 (cdslmd) GATEENSEMBLE_LOWEND GATEENSEMBLE_OPENDEV GATEENSEMBLE_OPENEXE

15:47:32 (cdslmd) GATEENSEMBLE_PA GATEENSEMBLE_PR_LE GATEENSEMBLE_PR_UL

15:47:32 (cdslmd) GATEENSEMBLE_QPLACE GATEENSEMBLE_QPLACE_TIMING GATEENSEMBLE_QROUTE

15:47:32 (cdslmd) GATEENSEMBLE_RGT GATEENSEMBLE_SCAN GATEENSEMBLE_TIMING

15:47:32 (cdslmd) GATEENSEMBLE_TIMING_LE GATEENSEMBLE_TIMING_UL GATEENSEMBLE_UNLIMITED

15:47:32 (cdslmd) Gate_Ensemble_WARP GATEENSEMBLE_WIDEWIRE gbom

15:47:32 (cdslmd) GDS_IF

GdsiiOut

GDT_IF

15:47:32 (cdslmd) ged2edif

glib

gloss

15:47:32 (cdslmd) gphysdly

gscald

GSM_Simulation_Runtime

15:47:32 (cdslmd) gspares

HDL-DESKTOP

hp3070

15:47:32 (cdslmd) HYB_2S10PUC_ALL HYB_2S15PUC_ALL HYB_2S20PUC_ALL

15:47:32 (cdslmd) HYB_2S40PUC_ALL HYB_2S60PUC_ALL HYB_4S40PUC_ALL

15:47:32 (cdslmd) HYB_4S60PUC_ALL HYB_4SUPUC_ALL

HYB_6S60PUC_ALL

15:47:32 (cdslmd) HYB_6S90PUC_ALL HYB_6SUPUC_ALL

IC_autoroute

15:47:32 (cdslmd) IC_autoroute_ALL IC_devicegen

IC_devicegen_ALL

15:47:32 (cdslmd) IC_deviceplace_ALL IC_edit

IC_edit_ALL

15:47:32 (cdslmd) IC_editfast_ALL Ice_Parallel

IC_gcell_route

15:47:32 (cdslmd) IC_gcell_route_ALL IC_hsrules

IC_hsrules_ALL

15:47:32 (cdslmd) IC_Inspector

IC_Inspector_ALL IC_InspectorEngr_ALL

15:47:32 (cdslmd) IC_mp_route

IC_mp_route_ALL IC_power_route

15:47:32 (cdslmd) IC_power_route_ALL IDF_Bi_Directional_Interface iges_electrical

15:47:32 (cdslmd) Incisive_Design_Team_Simulator Incisive_Desktop_Manager Incisive_Enterprise_Planner

15:47:32 (cdslmd) Incisive_Enterprise_Manager Incisive_Enterprise_Simulator Incisive_Formal_Verifier

15:47:32 (cdslmd) Incisive_HDL_Simulator Incisive_P2C_Methodology Incisive_Specman_interactive

15:47:32 (cdslmd) Incisive_Verif_Engine Incisive_Verif_Environ intrgloss

15:47:32 (cdslmd) Intrica_powerplane_builder intrroute

intrsignoise

15:47:32 (cdslmd) IPB_2S10PUC_ALL IPB_2S15PUC_ALL IPB_2S20PUC_ALL

15:47:32 (cdslmd) IPB_2S40PUC_ALL IPB_2S60PUC_ALL IPB_2SUPUC_ALL

15:47:32 (cdslmd) IPB_4S10PUC_ALL IPB_4S20PUC_ALL IPB_4S40PUC_ALL

15:47:32 (cdslmd) IPB_4S60PUC_ALL IPB_4SUPUC_ALL

IPB_6S60PUC_ALL

15:47:32 (cdslmd) IPB_6S90PUC_ALL IPB_6SUPUC_ALL

ipc_in

15:47:32 (cdslmd) ipc_out

IPlaceBase

IPlaceBase_ALL

15:47:32 (cdslmd) IPO

LAS_Cell_Optimization Layout

15:47:32 (cdslmd) LayoutEE

LayoutPlus

LEAPFROG-BV

15:47:32 (cdslmd) LEAPFROG-C

LEAPFROG-CV

LEAPFROG-SLAVE

15:47:32 (cdslmd) LEAPFROG-SV

LEAPFROG-SYS

LEFDEF_IF

15:47:32 (cdslmd) LID10

LID11

LINEAR_LIB

15:47:32 (cdslmd) LSE

lwb

MAG_LIB

15:47:32 (cdslmd) mdin

mdout

mdtoac

15:47:32 (cdslmd) mdtocv

MIXAD_LIB

Model_Check_Analysis

15:47:32 (cdslmd) MSMV

Multithread_Route_Option multiwire

15:47:32 (cdslmd) MV_4S40PUC_ALL

MV_6SUPUC_ALL

Nano_Encounter

15:47:32 (cdslmd) Nano_Encounter_DBS NanoRoute_Ultra NCSim_Desktop

15:47:32 (cdslmd) NC-simulator

nc_specman

ncsysc_specman

15:47:32 (cdslmd) NC_SystemC_Simulator NC_SystemVerilog_Simulator NC_Verilog_Compiler

15:47:32 (cdslmd) NC_Verilog_Data_Prep_Compiler NC_Verilog_Option NC_Verilog_Simulator

15:47:32 (cdslmd) NC_Vhdl_Compiler NC_Vhdl_Option

NC_Vhdl_Simulator

15:47:32 (cdslmd) NCVLOG_CGOPTS

NeoCell

Nihongoconcept

15:47:32 (cdslmd) OA

OASIS_RFDE

OASIS_Simulation_Interface

15:47:32 (cdslmd) odan

OpenModeler

OpenModeler_SFI

15:47:32 (cdslmd) OpenModeler_SWIFT OpenSim

OpenWaves

15:47:32 (cdslmd) Optimizer

OrCAD

OrCAD_PCB_Designer

15:47:32 (cdslmd) OrCAD_PCB_Designer_PSpice OrCAD_PCB_Router Pacific_Noise_Analyzer

15:47:32 (cdslmd) packager

PartitionOptimizer PAS_Assura_Drc_Generator

15:47:32 (cdslmd) PAS_Assura_Lvs_Generator PAS_Diva_Drc_Generator PAS_Diva_Lvs_Generator

15:47:32 (cdslmd) PAS_Dracula_Drc_Generator PAS_Dracula_Lvs_Generator PAS_ErrorCell_Generator

15:47:32 (cdslmd) PAS_Graphical_Tech_Editor PAS_Pcell_Generator PB_2S10PUC_ALL

15:47:32 (cdslmd) PB_2S15PUC_ALL

PB_2S20PUC_ALL

PB_2S40PUC_ALL

15:47:32 (cdslmd) PB_2S60PUC_ALL

PB_2SUPUC_ALL

PB_4S10PUC_ALL

15:47:32 (cdslmd) PB_4S40PUC_ALL

PB_4S60PUC_ALL

PB_4SUPUC_ALL

15:47:32 (cdslmd) PB_6S60PUC_ALL

PB_6SUPUC_ALL

PB_USUPUC_ALL

15:47:32 (cdslmd) PCB_designer

PCB_design_expert PCB_design_studio

15:47:32 (cdslmd) pcb_editor

pcb_engineer

pcb_interactive

15:47:32 (cdslmd) PCB_librarian_expert pcb_prep

pcb_review

15:47:32 (cdslmd) PCB_studio_variants pcomp

Pearl

15:47:32 (cdslmd) Pearl_Cell

PE_Librarian

Physical_Verification_Sys

15:47:32 (cdslmd) Physical_Verification_Sys_L Physical_Verification_Sys_XL Physical_Verification_Sys_Deb

15:47:32 (cdslmd) PICDesigner

PIC_Utilities

PKS

15:47:32 (cdslmd) PlaceBase

PlaceBase_ALL

placement

15:47:32 (cdslmd) Placement_Based_Optimization Placement_Based_Synthesis PlaceOrIPlace_ALL

15:47:32 (cdslmd) PLD

plotVersa

PowerAnalysis

15:47:32 (cdslmd) PowerIntegrity

PP_2SUPUC_ALL

PP_4S40PUC_ALL

15:47:32 (cdslmd) PP_4S60PUC_ALL

PP_6S60PUC_ALL

PP_6S90PUC_ALL

15:47:32 (cdslmd) PP_6SUPUC_ALL

PPRoute

PPRoute_ALL

15:47:32 (cdslmd) Prevail_Board_Designer Prevail_Correct_By_Design Prevail_Designer

15:47:32 (cdslmd) Preview_Synopsys_Interface Protel_IF

PSpice

15:47:32 (cdslmd) PspiceAA

PspiceAD

PSpiceBasics

15:47:32 (cdslmd) PSpiceStudio

ptc_in

ptc_out

15:47:32 (cdslmd) PWM_LIB

QPlace

QRC_Advanced_Analysis

15:47:32 (cdslmd) QRC_Advanced_Modeling quanticout

Quickturn_Model_Manager

15:47:32 (cdslmd) RapidPART

rapidsim

RB_2S10PUC_ALL

15:47:32 (cdslmd) RB_2S15PUC_ALL

RB_2S20PUC_ALL

RB_2S40PUC_ALL

15:47:32 (cdslmd) RB_2S60PUC_ALL

RB_2SUPUC_ALL

RB_4S10PUC_ALL

15:47:32 (cdslmd) RB_4S20PUC_ALL

RB_4S40PUC_ALL

RB_4S60PUC_ALL

15:47:32 (cdslmd) RB_4SUPUC_ALL

RB_6S60PUC_ALL

RB_6S90PUC_ALL

15:47:32 (cdslmd) RB_6SUPUC

RB_6SUPUC_ALL

RCExtraction

15:47:32 (cdslmd) RC-GXL

RC-L

realchiplm

15:47:32 (cdslmd) redifnet

RELXPERT

Route

15:47:32 (cdslmd) RouteADV

RouteADV_ALL

RouteBase

15:47:32 (cdslmd) RouteBase_ALL

RouteDF

RouteDFM

15:47:32 (cdslmd) RouteDFM_ALL

RouteFST

RouteFST_ALL

15:47:32 (cdslmd) RouteHYB

RouteHYB_ALL

RouteMin_ALL

15:47:32 (cdslmd) RouteMVIA_ALL

RouteOrEdit_ALL rt

15:47:32 (cdslmd) RTL_Compiler_Physical RTL_Compiler_RD RTL_Compiler_Ultra

15:47:32 (cdslmd) RTL_Compiler_Ultra_II_Option RTL_Compiler_Verification Schematic_Generator

15:47:32 (cdslmd) SDL_IF

sdrc_in

sdrc_out

15:47:32 (cdslmd) SDT_MODEL_MANAGER sepks

shapefill

15:47:32 (cdslmd) signal_explorer Signal_Integrity SignalIntegrity

15:47:32 (cdslmd) SignalStorm_Lib_Characterizer Signalstorm_NDC SignalStorm_Parallel_Sim

15:47:32 (cdslmd) signoise

SigNoiseCS

SigNoiseEngineer

15:47:32 (cdslmd) SigNoiseExpert

SigNoise_Float

SigNoiseStdDigLib

15:47:32 (cdslmd) Sigxp

sigxp_explorer

Sigxp_tier

15:47:32 (cdslmd) Sigxp_tier_EXPERT Silicon_Ensemble Silicon_Ensemble_CTS

15:47:32 (cdslmd) Silicon_Ensemble_DSM Silicon_Ensemble_DSM_Crosstalk Silicon_Ensemble_OpenDev

15:47:32 (cdslmd) Silicon_Ensemble_OpenExe Silicon_Ensemble_WARP SiliconQuest

15:47:32 (cdslmd) SiliconQuest_CTGen_Option Silicon_Synthesis_QPBS SimControl

15:47:32 (cdslmd) SimVision

SiP_Digital_Architect_GXL SiP_Digital_Architect_L

15:47:32 (cdslmd) SiP_Digital_Architect_XL SiP_Digital_Layout_GXL SiP_Digital_SI_XL

15:47:32 (cdslmd) SiP_RF_Architect_L SiP_RF_Architect_XL SiP_RF_Layout_GXL

15:47:32 (cdslmd) SI_Timing_Convergence SI_Timing_Convergence_VS skillDev

15:47:32 (cdslmd) soce

SOC_Encounter

SOC_Encounter_GPS

15:47:32 (cdslmd) SOC_Encounter_GXL SOC_Encounter_L SOC_Encounter_XL

15:47:32 (cdslmd) SONYBNTI

SPECCTRA_256U

SPECCTRA_6U

15:47:32 (cdslmd) SPECCTRA_ADV

SPECCTRA_APD

specctra_autoroute

15:47:32 (cdslmd) specctra_designer SPECCTRA_DFM

specctra_expert

15:47:32 (cdslmd) specctra_expert_system SPECCTRA_HP

specctra_pcb

15:47:32 (cdslmd) specctra_performance SPECCTRA_QE

SPECCTRAQuest

15:47:32 (cdslmd) SPECCTRAQuest_EE SPECCTRAQuest_Planner SPECCTRAQuest_SI_expert

15:47:32 (cdslmd) SPECCTRAQuest_signal_expert SPECCTRAQuest_signal_explorer SPECCTRA_Unison_PCB

15:47:32 (cdslmd) SPECCTRA_Unison_Ultra SPECCTRA_VT

SpecialRoute

15:47:32 (cdslmd) specman

SpectreBasic

Spectre_BTAHVMOS_Models

15:47:32 (cdslmd) Spectre_BTASOI_Models Spectre_Burst_AllegroSI SpectreHDL

15:47:32 (cdslmd) Spectre_NorTel_Models Spectre_Parallel_Analysis SpectreRF

15:47:32 (cdslmd) Spectre_Siemens_Models Spectre_ST_Models SPICE_IF

15:47:32 (cdslmd) SPW

SPW_BER_Sim

SPW_CGS_

15:47:32 (cdslmd) SPW_HLS

SPW_LSF_Link

SPW_MPX

15:47:32 (cdslmd) SPW_Smart_Antenna_Library SQ_Digital_Logic_SI_Lib SQ_FPGA_SI_Lib

15:47:32 (cdslmd) SQ_Memory_SI_Lib SQ_Microprocessor_SI_Lib stream_in

15:47:32 (cdslmd) stream_out

StudioPSpiceAD

STV90a

15:47:32 (cdslmd) Substrate_Coupling_Analysis Substrate_Noise_Analyst sv_surecov

15:47:32 (cdslmd) sv_suresight

swap

SWIFT

15:47:32 (cdslmd) sx

Synlink_Interface synSmartIF

15:47:32 (cdslmd) synSmartLib

synTiOpt

TANCELL

15:47:32 (cdslmd) Test_Design_Analysis Test_Design_ATPG_Plus Test_Design_Compression

15:47:32 (cdslmd) Test_Design_Generation Test_Design_Verification Test_Extension_Language

15:47:32 (cdslmd) Test_Mfg_Fault_Isolation TimingAnalysis

TimingBudget

15:47:32 (cdslmd) transformal_ltx TrialRoute

tscr

15:47:32 (cdslmd) tsTestGen

tsTestIntf

tsTSynVHDL

15:47:32 (cdslmd) tsTSynVLOG

tune

tw01

15:47:32 (cdslmd) tw02

UET

ULMdelta

15:47:32 (cdslmd) ULMecho

ULMhotel

ULMindia

15:47:32 (cdslmd) ULMjuliette

ULMmike

ULTRASIM

15:47:32 (cdslmd) Unison_SPECCTRA_4U UNISON_SPECCTRA_6U Universal_Smartpath

15:47:32 (cdslmd) v2e

Vampire_HDRC

Vampire_HLVS

15:47:32 (cdslmd) Vampire_MP

Vampire_RCX

Vampire_UI

15:47:32 (cdslmd) VB_2S10PUC_ALL

VB_2S15PUC_ALL

VB_2S20PUC_ALL

15:47:32 (cdslmd) VB_2S40PUC_ALL

VB_2S60PUC_ALL

VB_2SUPUC_ALL

15:47:32 (cdslmd) VB_4S10PUC_ALL

VB_4S20PUC_ALL

VB_4S40PUC_ALL

15:47:32 (cdslmd) VB_4S60PUC_ALL

VB_4SUPUC_ALL

VB_6S60PUC_ALL

15:47:32 (cdslmd) VB_6S90PUC_ALL

VB_6SUPUC

VB_6SUPUC_ALL

15:47:32 (cdslmd) VB_USUPUC_ALL

VCC_Editors

VCC_links_to_implementation

15:47:32 (cdslmd) VCC_Simulators

VCC_SW_Estimator VCR

15:47:32 (cdslmd) vc-signalscan

vc-signalscan-transaction vc-transaction-explorer

15:47:32 (cdslmd) verifault

Verif_Ckpit_Analysis_Env Verif_Ckpit_Runtime_Env

15:47:32 (cdslmd) Verify

Verilog_desktop VERILOG-SLAVE

15:47:32 (cdslmd) VERILOG-XL

Verilog_XL_Desktop Verilog_XL_Turbo_NT

15:47:32 (cdslmd) VERITIME

vgen

VHDL_desktop

15:47:32 (cdslmd) VHDLLink

viable

ViewBase

15:47:32 (cdslmd) ViewBase_ALL

ViewBaseEngr_ALL Virtuoso_Acceler_Parallel_L

15:47:32 (cdslmd) Virtuoso_Acceler_Parallel_XL Virtuoso_APS_MMSIM_LK virtuoso_chip_editor

15:47:32 (cdslmd) VIRTUOSO_CM_OPTION_FOR_VSDE Virtuoso_Constraint_API Virtuoso_Core_Characterizer

15:47:32 (cdslmd) Virtuoso_Core_Optimizer Virtuoso_custom_placer Virtuoso_custom_router

15:47:32 (cdslmd) Virtuoso_Digital_implement Virtuoso_Layout_Migrate Virtuoso_Layout_Suite_GX

15:47:32 (cdslmd) Virtuoso_Layout_Suite_GXL Virtuoso_Layout_Suite_L Virtuoso_Layout_Suite_XL

15:47:32 (cdslmd) Virtuoso_Multi_mode_Simulation Virtuoso_NeoCircuit_DFM Virtuoso_Phase_Designer

15:47:32 (cdslmd) Virtuoso_QRC_Extraction_GXL Virtuoso_QRC_Extraction_L Virtuoso_QRC_Extraction_XL

15:47:32 (cdslmd) Virtuoso_Schematic_Editor_GXL Virtuoso_Schematic_Editor_L Virtuoso_Schematic_Editor_XL

15:47:32 (cdslmd) Virtuoso_Schem_Option Virtuoso_SiI

VIRTUOSO_SPEC_DRIVEN_ENVIRO

15:47:32 (cdslmd) Virtuoso_Spectre Virtuoso_Spectre_GXL Virtuoso_Spectre_RF

15:47:32 (cdslmd) Virtuoso_Spectre_XL Virtuoso_Sprectre_GXL_MMSIM_LK Virtuoso_Turbo

15:47:32 (cdslmd) Virtuoso_Turbo_Basic Virtuoso_Visual_Analysis_XL Virtuoso_XL

15:47:32 (cdslmd) Virtuoso_XL_Basic visula_in

VITAL-XL

15:47:32 (cdslmd) vloglink

vmanager

VoltageStorm_Cell_Transistor2

15:47:32 (cdslmd) VoltageStorm_UI VXL-ALPHA

VXL-LMC-HW-IF

15:47:32 (cdslmd) VXL-SWITCH-RC

VXL-TURBO

VXL-VCW

15:47:32 (cdslmd) VXL-VET

VXL-VLS

VXL-VRA

15:47:32 (cdslmd) wedifsch

WinPlace

WireEdit

15:47:32 (cdslmd) WLAN_Simulation_Runtime X4ENC

xilCds

15:47:32 (cdslmd) xilComposerFE

xilConceptFE

xilEdif

15:47:32 (cdslmd) Xilinx_FPGA

15:47:32 (cdslmd)

15:47:32 (cdslmd) All FEATURE lines for cdslmd behave like INCREMENT lines

15:47:32 (cdslmd)

15:47:42 (cdslmd) Vendor daemon can't talk to lmgrd (Cannot connect to license server system. (-15,570:115 "Operation now in progress"))

15:47:42 (cdslmd) EXITING DUE TO SIGNAL 37

15:47:42 (lmgrd) cdslmd exited with status 37 (Communications error)

15:47:42 (lmgrd) Since this is an unknown status, license server

15:47:42 (lmgrd) manager (lmgrd) will attempt to re-start the vendor daemon.

15:47:42 (cdslmd) FLEXnet Licensing version v10.8.2.1 build 30341

15:47:42 (lmgrd) REStarted cdslmd (internet tcp_port 55316 pid 4936)

15:47:43 (cdslmd) Server started on localhost.localdomain for:

100

15:47:43 (cdslmd) 111

11300

11400

15:47:43 (cdslmd) 11701

11702

11703

15:47:43 (cdslmd) 11710

12110

12111

15:47:43 (cdslmd) 12121

12141

12141_64bit

15:47:43 (cdslmd) 12150

12500

14000

15:47:43 (cdslmd) 14010

14020

14030

15:47:43 (cdslmd) 14040

14060

14100

15:47:43 (cdslmd) 14101

14110

14111

15:47:43 (cdslmd) 14120

14130

14140

15:47:43 (cdslmd) 14400

14410

14420

15:47:43 (cdslmd) 200

20120

20121

15:47:43 (cdslmd) 20122

20123

20124

15:47:43 (cdslmd) 20127

20128

20220

15:47:43 (cdslmd) 20221

20222

20227

15:47:43 (cdslmd) 206

207

21000

15:47:43 (cdslmd) 21060

21200

21400

15:47:43 (cdslmd) 2141

_21900

21900

15:47:43 (cdslmd) 21920

223

224

15:47:43 (cdslmd) 22650

22800

22810

15:47:43 (cdslmd) 24015

24025

24100

15:47:43 (cdslmd) 24205

250

251

15:47:43 (cdslmd) 26000

274

276

15:47:43 (cdslmd) 278

279

283

15:47:43 (cdslmd) 300

3000

3001

15:47:43 (cdslmd) 30010

3002

300_64bit

15:47:43 (cdslmd) 3011

302

305

15:47:43 (cdslmd) 31000

311

3111

15:47:43 (cdslmd) 312

314

316

15:47:43 (cdslmd) 318

32015

32100

15:47:43 (cdslmd) 32101

32110

32120

15:47:43 (cdslmd) 32125

32130

32140

15:47:43 (cdslmd) 32150

32190

322

15:47:43 (cdslmd) 32500

32501

32502

15:47:43 (cdslmd) 32503

32505

32510

15:47:43 (cdslmd) 32520

32521

32530

15:47:43 (cdslmd) 32550

32600

32610

15:47:43 (cdslmd) 32620

32630

32640

15:47:43 (cdslmd) 32760

33000

33010

15:47:43 (cdslmd) 33011

33015

33016

15:47:43 (cdslmd) 33100

33300

33301

15:47:43 (cdslmd) 334

33500

33580

15:47:43 (cdslmd) 336

3405

34500

15:47:43 (cdslmd) 34510

34511

34530

15:47:43 (cdslmd) 34570

34580

35100

15:47:43 (cdslmd) 35200

360

362

15:47:43 (cdslmd) 365

365_64bit

370

15:47:43 (cdslmd) 371

37100

373

15:47:43 (cdslmd) 374

38500

38520

15:47:43 (cdslmd) 39000

39001

3D_FieldSolver_Engine

15:47:43 (cdslmd) 4000

40020

40030

15:47:43 (cdslmd) 40040

40500

41000

15:47:43 (cdslmd) 50000

50010

501

15:47:43 (cdslmd) 50110

50200

502A

15:47:43 (cdslmd) 5100

51022

51023

15:47:43 (cdslmd) 51060

51070

51170

15:47:43 (cdslmd) 550

570

61300

15:47:43 (cdslmd) 61400

681

7000

15:47:43 (cdslmd) 70000

70110

70110_64bit

15:47:43 (cdslmd) 70120

70120_64bit

70130

15:47:43 (cdslmd) 70510

70510_64_bit

70520

15:47:43 (cdslmd) 70520_64bit

71110

71110_64bit

15:47:43 (cdslmd) 71120

71130

71510

15:47:43 (cdslmd) 71520

72110

72120

15:47:43 (cdslmd) 72130

72131

72132

15:47:43 (cdslmd) 72133

72134

72135

15:47:43 (cdslmd) 72140

72150

727

15:47:43 (cdslmd) 728

729

730

15:47:43 (cdslmd) 730_64bit

733

73510

15:47:43 (cdslmd) 73520

761

780

15:47:43 (cdslmd) 780_64bit

900

9000

15:47:43 (cdslmd) 90001

920

940

15:47:43 (cdslmd) 945

950

95100

15:47:43 (cdslmd) 95115

95120

952

15:47:43 (cdslmd) 95200

95210

95220

15:47:43 (cdslmd) 95255

95300

95310

15:47:43 (cdslmd) 95320

95400

960

15:47:43 (cdslmd) 960_64bit

963

964

15:47:43 (cdslmd) 965

966

972

15:47:43 (cdslmd) 974

991

992

15:47:43 (cdslmd) 993

994

995

15:47:43 (cdslmd) a2dxf

aae-signalscan

aae-signalscan-transaction

15:47:43 (cdslmd) aae-transaction-explorer ABIT

Actel_FPGA

15:47:43 (cdslmd) actomd

ADE_ElectronStorm_Option ADE_VoltageStorm_Option

15:47:43 (cdslmd) ADV_2S10PUC_ALL ADV_2S15PUC_ALL ADV_2S20PUC_ALL

15:47:43 (cdslmd) ADV_2S40PUC_ALL ADV_2S60PUC_ALL ADV_2SUPUC_ALL

15:47:43 (cdslmd) ADV_4S10PUC_ALL ADV_4S20PUC_ALL ADV_4S40PUC_ALL

15:47:43 (cdslmd) ADV_4S60PUC_ALL ADV_4SUPUC_ALL

ADV_6S60PUC_ALL

15:47:43 (cdslmd) ADV_6S90PUC_ALL ADV_6SUPUC_ALL

Advanced_Cell_Placer

15:47:43 (cdslmd) advanced_package_designer Advanced_Pkg_Engineer_3D adv_package_designer_expert

15:47:43 (cdslmd) adv_package_engineer_expert Affirma_3rdParty_Sim_Interface Affirma_advanced_analysis_env

15:47:43 (cdslmd) Affirma_AMS_distrib_processing Affirma_ams_simulator Affirma_equivalence_checker

15:47:43 (cdslmd) Affirma_equiv_checker_prep Affirma_model_checker Affirma_model_packager_export

15:47:43 (cdslmd) Affirma_NC_Simulator Affirma_NC_VHDL_Desktop_Sim Affirma_RF_IC_package

15:47:43 (cdslmd) Affirma_RF_IC_package_modeler Affirma_RF_SPW_model_link affirma-signalscan

15:47:43 (cdslmd) affirma-signalscan-control affirma-signalscan-pro affirma-signalscan-schmatic

15:47:43 (cdslmd) affirma-signalscan-source affirma-signalscan-transaction Affirma_sim_analysis_env

15:47:43 (cdslmd) Affirma_transaction_analysis affirma-transaction-explorer Affirma_trans_logic_abstracter

15:47:43 (cdslmd) ALL_EBD

Allegro_CAD_Interface Allegro_Design_Editor_620

15:47:43 (cdslmd) Allegro_Designer Allegro_designer_suite Allegro_design_expert

15:47:43 (cdslmd) allegro_dfa

allegro_dfa_att Allegro_Expert

15:47:43 (cdslmd) Allegro_Librarian allegro_non_partner Allegro_Package_Designer_620

15:47:43 (cdslmd) Allegro_Package_SI_620 Allegro_Package_SI_620_Suite Allegro_PCB

15:47:43 (cdslmd) Allegro_PCB_Design_230 Allegro_PCB_Design_620 Allegro_PCB_Interface

15:47:43 (cdslmd) Allegro_PCB_Partitioning Allegro_PCB_RF

Allegro_PCB_Router_210

15:47:43 (cdslmd) Allegro_PCB_Router_230 Allegro_PCB_Router_610 Allegro_PCB_SI_230

15:47:43 (cdslmd) Allegro_PCB_SI_620 Allegro_PCB_SI_630 Allegro_PCB_SI_630_Suite

15:47:43 (cdslmd) Allegro_performance Allegro_Pkg_Designer_620_Suite allegroprance

15:47:43 (cdslmd) Allegro_studio

allegro_symbol

Allegro_Viewer_Plus

15:47:43 (cdslmd) Altera_MAX

Ambit_BuildGates Ambit_libcompile

15:47:43 (cdslmd) Ambit_RnD_option AMD_MACH

AmoebaPlace

15:47:43 (cdslmd) AMS_Designer_Link AMS_environment AMS_Methodology_Kit

15:47:43 (cdslmd) AMS_Option_to_Incisive Analog_Design_Environment_GXL Analog_Design_Environment_L

15:47:43 (cdslmd) Analog_Design_Environment_XL ANALOG_WORKBENCH APD

15:47:43 (cdslmd) Aptivia

archiver

arouter

15:47:43 (cdslmd) Artist_Optimizer Artist_Statistics Assura_DRC

15:47:43 (cdslmd) Assura_DV_design_rule_checker Assura_DV_LVS_checker Assura_DV_parasitic_extractor

15:47:43 (cdslmd) Assura_LVS

Assura_MP

Assura_OPC

15:47:43 (cdslmd) Assura_RCX

Assura_RCX_Adv_Process Assura_RCX-FS

15:47:43 (cdslmd) Assura_RCX-HF

Assura_RCX-MP

Assura_RCX-PL

15:47:43 (cdslmd) Assura_SI

Assura_SiMC

Assura_SI-TL

15:47:43 (cdslmd) Assura_SiVL

Assura_UI

Atmel_ATV

15:47:43 (cdslmd) AWB_Batch

AWB_BEHAVIOR

AWB_DIST_SIM

15:47:43 (cdslmd) AWB_MAGAZINE

AWB_MAGNETICS

AWB_MIX

15:47:43 (cdslmd) AWB_PPLOT

AWB_RESOLVE_OPT AWB_SIMULATOR

15:47:43 (cdslmd) AWB_SMOKE

AWB_SPICEPLUS

AWB_STATS

15:47:43 (cdslmd) Base_Digital_Body_Lib Base_Verilog_Lib BG

15:47:43 (cdslmd) BlockMaster_Characterizer BlockMaster_Optimizer BlockPlace

15:47:43 (cdslmd) BoardQuest_Designer BoardQuest_Team BOGUS

15:47:43 (cdslmd) BRDST_IF

BuildGates_Extreme Cadence_3D_Design_Viewer

15:47:43 (cdslmd) Cadence_chip_assembly_router CADIF_IF

caeviews

15:47:43 (cdslmd) cals_out

Capture

CaptureCIS

15:47:43 (cdslmd) Capture_CIS_Studio catia

cbds_in

15:47:43 (cdslmd) CCAR

CDMA_Simulation_Runtime cdxe_in

15:47:43 (cdslmd) CELL3

CELL3_ARO

CELL3_CROSSTALK

15:47:43 (cdslmd) CELL3_CTS

CELL3_DIST

CELL3_ECL

15:47:43 (cdslmd) CELL3_OPENDEV

CELL3_OPENEXE

CELL3_PA

15:47:43 (cdslmd) CELL3_PR

CELL3_QPLACE

CELL3_QPLACE_TIMING

15:47:43 (cdslmd) CELL3_QROUTE

CELL3_RGT

CELL3_SCAN

15:47:43 (cdslmd) CELL3_TIMING

CELL3_WIDEWIRE

celtic

15:47:43 (cdslmd) Celtic_Crosstalk_Analyzer Celtic_NDC

CHDL_DesignAccess

15:47:43 (cdslmd) CheckADV_ALL

CheckPlus

Checkplus_Expert

15:47:43 (cdslmd) Cierto_HW_design_sys_2000 Cierto_signal_proc_wrksys_2000 Cierto_SPW_CDMA_Library

15:47:43 (cdslmd) Cierto_SPW_comm_lib_flt_pt Cierto_SPW_comm_library_fxp_pt Cierto_SPW_GSM_VE

15:47:43 (cdslmd) Cierto_SPW_IS136_VE Cierto_SPW_link_to_Ambit_BG Cierto_SPW_link_to_NC_sim

15:47:43 (cdslmd) Cierto_SPW_model_manager Cierto_SPW_multimedia_kit Cierto_SPW_pcscdma_VE

15:47:43 (cdslmd) Cierto_Wireless_LAN_Library ClockSyn

Clock_Tree_Generation

15:47:43 (cdslmd) Cobra_Simulator comp

compose

15:47:43 (cdslmd) compose_autoplan compose_gcr

ComposerCheckPlus_AdvRules

15:47:43 (cdslmd) ComposerCheckPlus_Checker ComposerCheckPlus_RuleDev Composer_EDIF300_Connectivity

15:47:43 (cdslmd) Composer_EDIF300_Schematic Composer_Schematic_Generator Composer_Spectre_Sim_Solution

15:47:43 (cdslmd) compose_scells

compose_tlmr

compose_util

15:47:43 (cdslmd) concept

ConceptHDL

Concept_HDL_expert

15:47:43 (cdslmd) Concept_HDL_rules_checker Concept_HDL_studio conceptXPC

15:47:43 (cdslmd) ConcICe_Option

Conformal_Asic

Conformal_Constraint_Designer

15:47:43 (cdslmd) Conformal_Constraint_Dsgnr_XL Conformal_Custom conformal_datapath

15:47:43 (cdslmd) Conformal_ECO

Conformal_ECO_GXL Conformal_GXL

15:47:43 (cdslmd) conformal_ldd

conformal_lec

Conformal_Low_Power

15:47:43 (cdslmd) Conformal_Low_Power_GXL Conformal_LP_GXL conformal_lvr

15:47:43 (cdslmd) conformal_mem

Conformal_Ultra conformal_vhd

15:47:43 (cdslmd) conformal_vlg

Corners_Analysis cpe

15:47:43 (cdslmd) CP_Ele_Checks

CPF

cpte

15:47:43 (cdslmd) CPtoolkit

crefer

CTE

15:47:43 (cdslmd) cvtomd

CWAVES

CWB01

15:47:43 (cdslmd) CWB03

CWB04

CWB05

15:47:43 (cdslmd) Datapath_Preview_Option Datapath_Verilog Datapath_VHDL

15:47:43 (cdslmd) debug

DelayCal

DesignViewer

15:47:43 (cdslmd) Desktop_mgr

Device_Level_Placer Device_Level_Router

15:47:43 (cdslmd) DFM_2S10PUC_ALL DFM_2S15PUC_ALL DFM_2S20PUC_ALL

15:47:43 (cdslmd) DFM_2S40PUC_ALL DFM_2S60PUC_ALL DFM_2SUPUC_ALL

15:47:43 (cdslmd) DFM_4S10PUC_ALL DFM_4S20PUC_ALL DFM_4S40PUC_ALL

15:47:43 (cdslmd) DFM_4S60PUC_ALL DFM_4SUPUC_ALL

DFM_6S60PUC_ALL

15:47:43 (cdslmd) DFM_6S90PUC_ALL DFM_6SUPUC_ALL

DFM_Core_Technology

15:47:43 (cdslmd) dfsverifault

DISCRETE_LIB

Distributed_Dracula_Option

15:47:43 (cdslmd) DRAC2CORE

DRAC2DRC

DRAC2LVS

15:47:43 (cdslmd) DRAC3CORE

DRAC3DRC

DRAC3LVS

15:47:43 (cdslmd) DRACACCESS

DRACDIST

DRACERC

15:47:43 (cdslmd) DRACLAYDE

DRACLPE

DRACLVS

15:47:43 (cdslmd) DRACPG_E

DRACPLOT

DRACPRE

15:47:43 (cdslmd) DRACSLAVE

dracula_in

dxf2a

15:47:43 (cdslmd) e2v

EB_2S10PUC_ALL

EB_2S15PUC_ALL

15:47:43 (cdslmd) EB_2S20PUC_ALL

EB_2S40PUC_ALL

EB_2S60PUC_ALL

15:47:43 (cdslmd) EB_2SUPUC_ALL

EB_4S10PUC_ALL

EB_4S20PUC_ALL

15:47:43 (cdslmd) EB_4S40PUC_ALL

EB_4S60PUC_ALL

EB_4SUPUC_ALL

15:47:43 (cdslmd) EB_6S60PUC_ALL

EB_6S90PUC_ALL

EB_6SUPUC_ALL

15:47:43 (cdslmd) EBD_edit

EBD_floorplan

EBD_power

15:47:43 (cdslmd) eCapture

ECO

edif2ged

15:47:43 (cdslmd) EDIF_Netlist_Interface EDIF_Schematic_Interface EditBase

15:47:43 (cdslmd) EditBase_ALL

EditFST

EditFST_ALL

15:47:43 (cdslmd) EditPlace_ALL

EditRoute_ALL

EF_2SUPUC_ALL

15:47:43 (cdslmd) EF_4S40PUC_ALL

EF_4S60PUC_ALL

EF_4SUPUC_ALL

15:47:43 (cdslmd) EF_6S60PUC_ALL

EF_6S90PUC_ALL

EF_6SUPUC_ALL

15:47:43 (cdslmd) EMCdisplay

EMControl

EMControl_Float

15:47:43 (cdslmd) EMI_ALL

Encounter

Encounter_Adv_Node_GXL

15:47:43 (cdslmd) Encounter_C

Encounter_ClockSyn Encounter_Digital_Impl_Sys_L

15:47:43 (cdslmd) Encounter_Digital_Impl_Sys_XL Encounter_Low_Power_GXL Encounter_Mixed_Signal_GXL

15:47:43 (cdslmd) Encounter_QRC_Extraction_GXL Encounter_QRC_Extraction_L Encounter_QRC_Extraction_XL

15:47:43 (cdslmd) Encounter_Test_Architect Encounter_Timing_System_L Encounter_Timing_System_XL

15:47:43 (cdslmd) Encounter_True_Time Encounter_Wave_Viewer Encounter_X

15:47:43 (cdslmd) Envisia_DataPath_option Envisia_GE_ultra_place_route Envisia_LowPower_option

15:47:43 (cdslmd) Envisia_PKS

Envisia_RAC

Envisia_SE_SI_place_route

15:47:43 (cdslmd) Envisia_SE_ultra_place_route Envisia_Utility evc_verisity_ahb

15:47:43 (cdslmd) evc_verisity_axi evc_verisity_enet evc_verisity_pci

15:47:43 (cdslmd) evc_verisity_pcie evc_verisity_pcie_ep evc_verisity_pcie_rc

15:47:43 (cdslmd) evc_verisity_usb evc_verisity_usb_otg expert

15:47:43 (cdslmd) expgen

explorer

Express

15:47:43 (cdslmd) ExpressPlus

Extended_Digital_Body_Lib Extended_Digital_Lib

15:47:43 (cdslmd) Extended_Verilog_Lib fcengine

fcheck

15:47:43 (cdslmd) FE_ASIC

FE_ASIC_Agere

FE_ASIC_Fujitsu

15:47:43 (cdslmd) FE_ASIC_IBM

FE_ASIC_LSILogic FE_ASIC_Mitsubishi

15:47:43 (cdslmd) FE_ASIC_NEC

FE_ASIC_Philips FE_ASIC_Samsung

15:47:43 (cdslmd) FE_ASIC_ST

FE_ASIC_TI

FE_ASIC_Toshiba

15:47:43 (cdslmd) FE_Classic

FE_GPS

fethman

15:47:43 (cdslmd) fetsetup

FE_Ultra

Fire_Ice_Cell

15:47:43 (cdslmd) Fire_Ice_Cell_Transistor Fire_IceQXC2_Cell Fire_Parallel

15:47:43 (cdslmd) FirstEncounter

First_Encounter_GPS First_Encounter_GXL

15:47:43 (cdslmd) FirstEncounterSOC First_Encounter_Ultra First_Encounter_VIP

15:47:43 (cdslmd) First_Encounter_XL FloatPC_ALL

FloorPlan

15:47:43 (cdslmd) fluke

FPGA_Flows

FPGA_OPTIMIZER

15:47:43 (cdslmd) FPGA_Tools

Framework

fsim

15:47:43 (cdslmd) FST_2SUPUC_ALL

FST_4S40PUC_ALL FST_4S60PUC_ALL

15:47:43 (cdslmd) FST_4SUPUC_ALL

FST_6S60PUC_ALL FST_6S90PUC_ALL

15:47:43 (cdslmd) FST_6SUPUC_ALL

FUNCTION_LIB

GATEENSEMBLE

15:47:43 (cdslmd) GATEENSEMBLE_ARO GATEENSEMBLE_CROSSTALK GATEENSEMBLE_CTS

15:47:43 (cdslmd) GATEENSEMBLE_CTS_LE GATEENSEMBLE_CTS_UL GATEENSEMBLE_DIST

15:47:43 (cdslmd) Gate_Ensemble_DSM Gate_Ensemble_DSM_Crosstalk GATEENSEMBLE_ECL

15:47:43 (cdslmd) GATEENSEMBLE_LOWEND GATEENSEMBLE_OPENDEV GATEENSEMBLE_OPENEXE

15:47:43 (cdslmd) GATEENSEMBLE_PA GATEENSEMBLE_PR_LE GATEENSEMBLE_PR_UL

15:47:43 (cdslmd) GATEENSEMBLE_QPLACE GATEENSEMBLE_QPLACE_TIMING GATEENSEMBLE_QROUTE

15:47:43 (cdslmd) GATEENSEMBLE_RGT GATEENSEMBLE_SCAN GATEENSEMBLE_TIMING

15:47:43 (cdslmd) GATEENSEMBLE_TIMING_LE GATEENSEMBLE_TIMING_UL GATEENSEMBLE_UNLIMITED

15:47:43 (cdslmd) Gate_Ensemble_WARP GATEENSEMBLE_WIDEWIRE gbom

15:47:43 (cdslmd) GDS_IF

GdsiiOut

GDT_IF

15:47:43 (cdslmd) ged2edif

glib

gloss

15:47:43 (cdslmd) gphysdly

gscald

GSM_Simulation_Runtime

15:47:43 (cdslmd) gspares

HDL-DESKTOP

hp3070

15:47:43 (cdslmd) HYB_2S10PUC_ALL HYB_2S15PUC_ALL HYB_2S20PUC_ALL

15:47:43 (cdslmd) HYB_2S40PUC_ALL HYB_2S60PUC_ALL HYB_4S40PUC_ALL

15:47:43 (cdslmd) HYB_4S60PUC_ALL HYB_4SUPUC_ALL

HYB_6S60PUC_ALL

15:47:43 (cdslmd) HYB_6S90PUC_ALL HYB_6SUPUC_ALL

IC_autoroute

15:47:43 (cdslmd) IC_autoroute_ALL IC_devicegen

IC_devicegen_ALL

15:47:43 (cdslmd) IC_deviceplace_ALL IC_edit

IC_edit_ALL

15:47:43 (cdslmd) IC_editfast_ALL Ice_Parallel

IC_gcell_route

15:47:43 (cdslmd) IC_gcell_route_ALL IC_hsrules

IC_hsrules_ALL

15:47:43 (cdslmd) IC_Inspector

IC_Inspector_ALL IC_InspectorEngr_ALL

15:47:43 (cdslmd) IC_mp_route

IC_mp_route_ALL IC_power_route

15:47:43 (cdslmd) IC_power_route_ALL IDF_Bi_Directional_Interface iges_electrical

15:47:43 (cdslmd) Incisive_Design_Team_Simulator Incisive_Desktop_Manager Incisive_Enterprise_Planner

15:47:43 (cdslmd) Incisive_Enterprise_Manager Incisive_Enterprise_Simulator Incisive_Formal_Verifier

15:47:43 (cdslmd) Incisive_HDL_Simulator Incisive_P2C_Methodology Incisive_Specman_interactive

15:47:43 (cdslmd) Incisive_Verif_Engine Incisive_Verif_Environ intrgloss

15:47:43 (cdslmd) Intrica_powerplane_builder intrroute

intrsignoise

15:47:43 (cdslmd) IPB_2S10PUC_ALL IPB_2S15PUC_ALL IPB_2S20PUC_ALL

15:47:43 (cdslmd) IPB_2S40PUC_ALL IPB_2S60PUC_ALL IPB_2SUPUC_ALL

15:47:43 (cdslmd) IPB_4S10PUC_ALL IPB_4S20PUC_ALL IPB_4S40PUC_ALL

15:47:43 (cdslmd) IPB_4S60PUC_ALL IPB_4SUPUC_ALL

IPB_6S60PUC_ALL

15:47:43 (cdslmd) IPB_6S90PUC_ALL IPB_6SUPUC_ALL

ipc_in

15:47:43 (cdslmd) ipc_out

IPlaceBase

IPlaceBase_ALL

15:47:43 (cdslmd) IPO

LAS_Cell_Optimization Layout

15:47:43 (cdslmd) LayoutEE

LayoutPlus

LEAPFROG-BV

15:47:43 (cdslmd) LEAPFROG-C

LEAPFROG-CV

LEAPFROG-SLAVE

15:47:43 (cdslmd) LEAPFROG-SV

LEAPFROG-SYS

LEFDEF_IF

15:47:43 (cdslmd) LID10

LID11

LINEAR_LIB

15:47:43 (cdslmd) LSE

lwb

MAG_LIB

15:47:43 (cdslmd) mdin

mdout

mdtoac

15:47:43 (cdslmd) mdtocv

MIXAD_LIB

Model_Check_Analysis

15:47:43 (cdslmd) MSMV

Multithread_Route_Option multiwire

15:47:43 (cdslmd) MV_4S40PUC_ALL

MV_6SUPUC_ALL

Nano_Encounter

15:47:43 (cdslmd) Nano_Encounter_DBS NanoRoute_Ultra NCSim_Desktop

15:47:43 (cdslmd) NC-simulator

nc_specman

ncsysc_specman

15:47:43 (cdslmd) NC_SystemC_Simulator NC_SystemVerilog_Simulator NC_Verilog_Compiler

15:47:43 (cdslmd) NC_Verilog_Data_Prep_Compiler NC_Verilog_Option NC_Verilog_Simulator

15:47:43 (cdslmd) NC_Vhdl_Compiler NC_Vhdl_Option

NC_Vhdl_Simulator

15:47:43 (cdslmd) NCVLOG_CGOPTS

NeoCell

Nihongoconcept

15:47:43 (cdslmd) OA

OASIS_RFDE

OASIS_Simulation_Interface

15:47:43 (cdslmd) odan

OpenModeler

OpenModeler_SFI

15:47:43 (cdslmd) OpenModeler_SWIFT OpenSim

OpenWaves

15:47:43 (cdslmd) Optimizer

OrCAD

OrCAD_PCB_Designer

15:47:43 (cdslmd) OrCAD_PCB_Designer_PSpice OrCAD_PCB_Router Pacific_Noise_Analyzer

15:47:43 (cdslmd) packager

PartitionOptimizer PAS_Assura_Drc_Generator

15:47:43 (cdslmd) PAS_Assura_Lvs_Generator PAS_Diva_Drc_Generator PAS_Diva_Lvs_Generator

15:47:43 (cdslmd) PAS_Dracula_Drc_Generator PAS_Dracula_Lvs_Generator PAS_ErrorCell_Generator

15:47:43 (cdslmd) PAS_Graphical_Tech_Editor PAS_Pcell_Generator PB_2S10PUC_ALL

15:47:43 (cdslmd) PB_2S15PUC_ALL

PB_2S20PUC_ALL

PB_2S40PUC_ALL

15:47:43 (cdslmd) PB_2S60PUC_ALL

PB_2SUPUC_ALL

PB_4S10PUC_ALL

15:47:43 (cdslmd) PB_4S40PUC_ALL

PB_4S60PUC_ALL

PB_4SUPUC_ALL

15:47:43 (cdslmd) PB_6S60PUC_ALL

PB_6SUPUC_ALL

PB_USUPUC_ALL

15:47:43 (cdslmd) PCB_designer

PCB_design_expert PCB_design_studio

15:47:43 (cdslmd) pcb_editor

pcb_engineer

pcb_interactive

15:47:43 (cdslmd) PCB_librarian_expert pcb_prep

pcb_review

15:47:43 (cdslmd) PCB_studio_variants pcomp

Pearl

15:47:43 (cdslmd) Pearl_Cell

PE_Librarian

Physical_Verification_Sys

15:47:43 (cdslmd) Physical_Verification_Sys_L Physical_Verification_Sys_XL Physical_Verification_Sys_Deb

15:47:43 (cdslmd) PICDesigner

PIC_Utilities

PKS

15:47:43 (cdslmd) PlaceBase

PlaceBase_ALL

placement

15:47:43 (cdslmd) Placement_Based_Optimization Placement_Based_Synthesis PlaceOrIPlace_ALL

15:47:43 (cdslmd) PLD

plotVersa

PowerAnalysis

15:47:43 (cdslmd) PowerIntegrity

PP_2SUPUC_ALL

PP_4S40PUC_ALL

15:47:43 (cdslmd) PP_4S60PUC_ALL

PP_6S60PUC_ALL

PP_6S90PUC_ALL

15:47:43 (cdslmd) PP_6SUPUC_ALL

PPRoute

PPRoute_ALL

15:47:43 (cdslmd) Prevail_Board_Designer Prevail_Correct_By_Design Prevail_Designer

15:47:43 (cdslmd) Preview_Synopsys_Interface Protel_IF

PSpice

15:47:43 (cdslmd) PspiceAA

PspiceAD

PSpiceBasics

15:47:43 (cdslmd) PSpiceStudio

ptc_in

ptc_out

15:47:43 (cdslmd) PWM_LIB

QPlace

QRC_Advanced_Analysis

15:47:43 (cdslmd) QRC_Advanced_Modeling quanticout

Quickturn_Model_Manager

15:47:43 (cdslmd) RapidPART

rapidsim

RB_2S10PUC_ALL

15:47:43 (cdslmd) RB_2S15PUC_ALL

RB_2S20PUC_ALL

RB_2S40PUC_ALL

15:47:43 (cdslmd) RB_2S60PUC_ALL

RB_2SUPUC_ALL

RB_4S10PUC_ALL

15:47:43 (cdslmd) RB_4S20PUC_ALL

RB_4S40PUC_ALL

RB_4S60PUC_ALL

15:47:43 (cdslmd) RB_4SUPUC_ALL

RB_6S60PUC_ALL

RB_6S90PUC_ALL

15:47:43 (cdslmd) RB_6SUPUC

RB_6SUPUC_ALL

RCExtraction

15:47:43 (cdslmd) RC-GXL

RC-L

realchiplm

15:47:43 (cdslmd) redifnet

RELXPERT

Route

15:47:43 (cdslmd) RouteADV

RouteADV_ALL

RouteBase

15:47:43 (cdslmd) RouteBase_ALL

RouteDF

RouteDFM

15:47:43 (cdslmd) RouteDFM_ALL

RouteFST

RouteFST_ALL

15:47:43 (cdslmd) RouteHYB

RouteHYB_ALL

RouteMin_ALL

15:47:43 (cdslmd) RouteMVIA_ALL

RouteOrEdit_ALL rt

15:47:43 (cdslmd) RTL_Compiler_Physical RTL_Compiler_RD RTL_Compiler_Ultra

15:47:43 (cdslmd) RTL_Compiler_Ultra_II_Option RTL_Compiler_Verification Schematic_Generator

15:47:43 (cdslmd) SDL_IF

sdrc_in

sdrc_out

15:47:43 (cdslmd) SDT_MODEL_MANAGER sepks

shapefill

15:47:43 (cdslmd) signal_explorer Signal_Integrity SignalIntegrity

15:47:43 (cdslmd) SignalStorm_Lib_Characterizer Signalstorm_NDC SignalStorm_Parallel_Sim

15:47:43 (cdslmd) signoise

SigNoiseCS

SigNoiseEngineer

15:47:43 (cdslmd) SigNoiseExpert

SigNoise_Float

SigNoiseStdDigLib

15:47:43 (cdslmd) Sigxp

sigxp_explorer

Sigxp_tier

15:47:43 (cdslmd) Sigxp_tier_EXPERT Silicon_Ensemble Silicon_Ensemble_CTS

15:47:43 (cdslmd) Silicon_Ensemble_DSM Silicon_Ensemble_DSM_Crosstalk Silicon_Ensemble_OpenDev

15:47:43 (cdslmd) Silicon_Ensemble_OpenExe Silicon_Ensemble_WARP SiliconQuest

15:47:43 (cdslmd) SiliconQuest_CTGen_Option Silicon_Synthesis_QPBS SimControl

15:47:43 (cdslmd) SimVision

SiP_Digital_Architect_GXL SiP_Digital_Architect_L

15:47:43 (cdslmd) SiP_Digital_Architect_XL SiP_Digital_Layout_GXL SiP_Digital_SI_XL

15:47:43 (cdslmd) SiP_RF_Architect_L SiP_RF_Architect_XL SiP_RF_Layout_GXL

15:47:43 (cdslmd) SI_Timing_Convergence SI_Timing_Convergence_VS skillDev

15:47:43 (cdslmd) soce

SOC_Encounter

SOC_Encounter_GPS

15:47:43 (cdslmd) SOC_Encounter_GXL SOC_Encounter_L SOC_Encounter_XL

15:47:43 (cdslmd) SONYBNTI

SPECCTRA_256U

SPECCTRA_6U

15:47:43 (cdslmd) SPECCTRA_ADV

SPECCTRA_APD

specctra_autoroute

15:47:43 (cdslmd) specctra_designer SPECCTRA_DFM

specctra_expert

15:47:43 (cdslmd) specctra_expert_system SPECCTRA_HP

specctra_pcb

15:47:43 (cdslmd) specctra_performance SPECCTRA_QE

SPECCTRAQuest

15:47:43 (cdslmd) SPECCTRAQuest_EE SPECCTRAQuest_Planner SPECCTRAQuest_SI_expert

15:47:43 (cdslmd) SPECCTRAQuest_signal_expert SPECCTRAQuest_signal_explorer SPECCTRA_Unison_PCB

15:47:43 (cdslmd) SPECCTRA_Unison_Ultra SPECCTRA_VT

SpecialRoute

15:47:43 (cdslmd) specman

SpectreBasic

Spectre_BTAHVMOS_Models

15:47:43 (cdslmd) Spectre_BTASOI_Models Spectre_Burst_AllegroSI SpectreHDL

15:47:43 (cdslmd) Spectre_NorTel_Models Spectre_Parallel_Analysis SpectreRF

15:47:43 (cdslmd) Spectre_Siemens_Models Spectre_ST_Models SPICE_IF

15:47:43 (cdslmd) SPW

SPW_BER_Sim

SPW_CGS_

15:47:43 (cdslmd) SPW_HLS

SPW_LSF_Link

SPW_MPX

15:47:43 (cdslmd) SPW_Smart_Antenna_Library SQ_Digital_Logic_SI_Lib SQ_FPGA_SI_Lib

15:47:43 (cdslmd) SQ_Memory_SI_Lib SQ_Microprocessor_SI_Lib stream_in

15:47:43 (cdslmd) stream_out

StudioPSpiceAD

STV90a

15:47:43 (cdslmd) Substrate_Coupling_Analysis Substrate_Noise_Analyst sv_surecov

15:47:43 (cdslmd) sv_suresight

swap

SWIFT

15:47:43 (cdslmd) sx

Synlink_Interface synSmartIF

15:47:43 (cdslmd) synSmartLib

synTiOpt

TANCELL

15:47:43 (cdslmd) Test_Design_Analysis Test_Design_ATPG_Plus Test_Design_Compression

15:47:43 (cdslmd) Test_Design_Generation Test_Design_Verification Test_Extension_Language

15:47:43 (cdslmd) Test_Mfg_Fault_Isolation TimingAnalysis

TimingBudget

15:47:43 (cdslmd) transformal_ltx TrialRoute

tscr

15:47:43 (cdslmd) tsTestGen

tsTestIntf

tsTSynVHDL

15:47:43 (cdslmd) tsTSynVLOG

tune

tw01

15:47:43 (cdslmd) tw02

UET

ULMdelta

15:47:43 (cdslmd) ULMecho

ULMhotel

ULMindia

15:47:43 (cdslmd) ULMjuliette

ULMmike

ULTRASIM

15:47:43 (cdslmd) Unison_SPECCTRA_4U UNISON_SPECCTRA_6U Universal_Smartpath

15:47:43 (cdslmd) v2e

Vampire_HDRC

Vampire_HLVS

15:47:43 (cdslmd) Vampire_MP

Vampire_RCX

Vampire_UI

15:47:43 (cdslmd) VB_2S10PUC_ALL

VB_2S15PUC_ALL

VB_2S20PUC_ALL

15:47:43 (cdslmd) VB_2S40PUC_ALL

VB_2S60PUC_ALL

VB_2SUPUC_ALL

15:47:43 (cdslmd) VB_4S10PUC_ALL

VB_4S20PUC_ALL

VB_4S40PUC_ALL

15:47:43 (cdslmd) VB_4S60PUC_ALL

VB_4SUPUC_ALL

VB_6S60PUC_ALL

15:47:43 (cdslmd) VB_6S90PUC_ALL

VB_6SUPUC

VB_6SUPUC_ALL

15:47:43 (cdslmd) VB_USUPUC_ALL

VCC_Editors

VCC_links_to_implementation

15:47:43 (cdslmd) VCC_Simulators

VCC_SW_Estimator VCR

15:47:43 (cdslmd) vc-signalscan

vc-signalscan-transaction vc-transaction-explorer

15:47:43 (cdslmd) verifault

Verif_Ckpit_Analysis_Env Verif_Ckpit_Runtime_Env

15:47:43 (cdslmd) Verify

Verilog_desktop VERILOG-SLAVE

15:47:43 (cdslmd) VERILOG-XL

Verilog_XL_Desktop Verilog_XL_Turbo_NT

15:47:43 (cdslmd) VERITIME

vgen

VHDL_desktop

15:47:43 (cdslmd) VHDLLink

viable

ViewBase

15:47:43 (cdslmd) ViewBase_ALL

ViewBaseEngr_ALL Virtuoso_Acceler_Parallel_L

15:47:43 (cdslmd) Virtuoso_Acceler_Parallel_XL Virtuoso_APS_MMSIM_LK virtuoso_chip_editor

15:47:43 (cdslmd) VIRTUOSO_CM_OPTION_FOR_VSDE Virtuoso_Constraint_API Virtuoso_Core_Characterizer

15:47:43 (cdslmd) Virtuoso_Core_Optimizer Virtuoso_custom_placer Virtuoso_custom_router

15:47:43 (cdslmd) Virtuoso_Digital_implement Virtuoso_Layout_Migrate Virtuoso_Layout_Suite_GX

15:47:43 (cdslmd) Virtuoso_Layout_Suite_GXL Virtuoso_Layout_Suite_L Virtuoso_Layout_Suite_XL

15:47:43 (cdslmd) Virtuoso_Multi_mode_Simulation Virtuoso_NeoCircuit_DFM Virtuoso_Phase_Designer

15:47:43 (cdslmd) Virtuoso_QRC_Extraction_GXL Virtuoso_QRC_Extraction_L Virtuoso_QRC_Extraction_XL

15:47:43 (cdslmd) Virtuoso_Schematic_Editor_GXL Virtuoso_Schematic_Editor_L Virtuoso_Schematic_Editor_XL

15:47:43 (cdslmd) Virtuoso_Schem_Option Virtuoso_SiI

VIRTUOSO_SPEC_DRIVEN_ENVIRO

15:47:43 (cdslmd) Virtuoso_Spectre Virtuoso_Spectre_GXL Virtuoso_Spectre_RF

15:47:43 (cdslmd) Virtuoso_Spectre_XL Virtuoso_Sprectre_GXL_MMSIM_LK Virtuoso_Turbo

15:47:43 (cdslmd) Virtuoso_Turbo_Basic Virtuoso_Visual_Analysis_XL Virtuoso_XL

15:47:43 (cdslmd) Virtuoso_XL_Basic visula_in

VITAL-XL

15:47:43 (cdslmd) vloglink

vmanager

VoltageStorm_Cell_Transistor2

15:47:43 (cdslmd) VoltageStorm_UI VXL-ALPHA

VXL-LMC-HW-IF

15:47:43 (cdslmd) VXL-SWITCH-RC

VXL-TURBO

VXL-VCW

15:47:43 (cdslmd) VXL-VET

VXL-VLS

VXL-VRA

15:47:43 (cdslmd) wedifsch

WinPlace

WireEdit

15:47:43 (cdslmd) WLAN_Simulation_Runtime X4ENC

xilCds

15:47:43 (cdslmd) xilComposerFE

xilConceptFE

xilEdif

15:47:43 (cdslmd) Xilinx_FPGA

15:47:43 (cdslmd)

15:47:43 (cdslmd) All FEATURE lines for cdslmd behave like INCREMENT lines

15:47:43 (cdslmd)

15:47:53 (cdslmd) Vendor daemon can't talk to lmgrd (Cannot connect to license server system. (-15,570:115 "Operation now in progress"))

15:47:53 (cdslmd) EXITING DUE TO SIGNAL 37

求大神指点哦,坐等大神哦

坐等高手哦,高手快快现身吧

坐等高手哦,高手快快现身吧

顶了!下来看看。

Is it the universal crack flow for other cadence tools?

感谢分享!多多学习!